**ACSP** · Analog Circuits And Signal Processing

Hakan Kuntman Deniz Özenli Fırat Kaçar Yasin Özçelep

# Reliability of CMOS Analog ICs

# **Analog Circuits and Signal Processing**

### **Series Editors**

Mohammed Ismail, Khalifa University, Dublin, USA Mohamad Sawan, 18, Shilongshan Road, School of Engineering, Westlake University, Hangzhou, Canada The Analog Circuits and Signal Processing book series, formerly known as the Kluwer International Series in Engineering and Computer Science, is a high level academic and professional series publishing research on the design and applications of analog integrated circuits and signal processing circuits and systems. Typically per year we publish between 5-15 research monographs, professional books, handbooks, and edited volumes with worldwide distribution to engineers, researchers, educators, and libraries. The book series promotes and expedites the dissemination of new research results and tutorial views in the analog field. There is an exciting and large volume of research activity in the field worldwide. Researchers are striving to bridge the gap between classical analog work and recent advances in very large scale integration (VLSI) technologies with improved analog capabilities. Analog VLSI has been recognized as a major technology for future information processing. Analog work is showing signs of dramatic changes with emphasis on interdisciplinary research efforts combining device/circuit/technology issues. Consequently, new design concepts, strategies and design tools are being unveiled. Topics of interest include: Analog Interface Circuits and Systems; Data converters; Active-RC, switched-capacitor continuous-time and filters; Mixed analog/digital VLSI; Simulation and modeling, mixed-mode simulation; Analog nonlinear and computational circuits and signal processing; Analog Artificial Neural Networks/Artificial Intelligence; Current-mode Signal Processing; Computer-Aided Design (CAD) tools; Analog Design in emerging technologies (Scalable CMOS, BiCMOS, GaAs, heterojunction and floating gate technologies, etc.); Analog Design for Test; Integrated sensors and actuators; Analog Design Automation/Knowledge-based Systems; Analog VLSI cell libraries; Analog product development; RF Front ends, Wireless communications and Circuits; Analog behavioral modeling, Analog HDL.

Hakan Kuntman • Deniz Özenli Fırat Kaçar • Yasin Özçelep

# Reliability of CMOS Analog ICs

Hakan Kuntman Istanbul Technical University Maslak/Istanbul, Türkiye

Fırat Kaçar Istanbul University - Cerrahpaşa Avcılar/İstanbul, Türkiye Deniz Özenli National Defense University Yeşilyurt/Istanbul, Türkiye

Yasin Özçelep Istanbul University - Cerrahpaşa Avcılar/İstanbul, Türkiye

ISSN 1872-082X ISSN 2197-1854 (electronic)

Analog Circuits and Signal Processing

ISBN 978-3-031-85454-5 ISBN 978-3-031-85455-2 (eBook)

https://doi.org/10.1007/978-3-031-85455-2

$\ \odot$  The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Switzerland AG 2025

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

If disposing of this product, please recycle the paper.

# **Preface**

The use of statistical approach for reliable and optimal design of systems, including electronic systems, has become quite popular. Statistically designed experiments/simulations have been used extensively for estimating or demonstrating existing reliability by identifying the important parameters (factors) affecting reliability out of many potentially important ones. This statistical approach ensures the performance and safety of critical electronic systems employed in space, nuclear, automotive, defence industry, submarine, and aerospace applications, to name a few.

In most reliability studies on modeling the hot-carrier effect available in the literature, models based on physical properties have been proposed; however, difficulties in preparation of physical models, losing the actuality within the advances in the technology, and excessively long simulation times seem to be disadvantages of these models.

To overcome these disadvantages of physical models, statistical methods based on the observation results, independent of the technology, and exhibiting a short simulation time and high accuracy have been introduced in our work.

Although digital signal processing is becoming increasingly more powerful and many types of signal processing have indeed moved to digital domain due to the advances in IC technology, analog circuits are fundamentally necessary in many complex and high performance systems. This is caused by the fact that naturally occurring signals are analog. In other words, analog circuits act as a bridge between the real world and digital systems. In analog signal processing, many circuit topologies including active filters, oscillators, immittance simulators, etc. have been proposed in the literature. Application area of analog signal processing is wide and ranges from very low frequencies at several Hz levels to RF applications operating at GHz level, which means from biomedical and sonar signals to cognitive radio and encrypted communications. Today, modern CMOS technologies are continuously scaling down; but as a result of this, analog designers have serious reliability problems in their designs caused by physical effects.

This book gives a review of our previously performed and published works in the open literature on statistical method-based modeling of the experimental studies on degradation in the drain current and threshold voltage of the NMOS and PMOS

vi Preface

transistors, including power MOSFETs. All these works were performed by our research group in the frame of Ph.D. and M.Sc. thesis works in Istanbul University and Istanbul Technical University. Note that these models are based on the observations by operating the device under stress voltage conditions.

We believe that this book will be useful for analog circuit designers working in the related area and provides a simple and useful alternative to physical methods available in the literature.

Istanbul, Turkey Istanbul, Turkey Istanbul, Turkey Istanbul, Turkey Hakan Kuntman Deniz Özenli Fırat Kaçar Yasin Özçelep

# **Dedication to Ayten Kuntman**

## In loving memory of Prof. Dr. Ayten Kuntman (1956–2023)

We started actually with Prof. Dr. Ayten Kuntman to prepare this book, where she was one of the authors of the works performed; unfortunately, we lost Prof. Kuntman in 2023. We continued with other colleagues, two are her former Ph.D. and M.Sc. students in the research group; they are also coauthors of these works.

We always remember her name and her contribution to this book.

Istanbul, Turkey Hakan Kuntman

# **Contents**

| 1 | Introduction. References.                                  | 1 3 |

|---|------------------------------------------------------------|-----|

| • |                                                            | 3   |

| 2 | The Reliability Model for PMOS and NMOS                    | 7   |

|   | Transistors Based on Statistical Methods                   | 7   |

|   | Basic Concepts: Reliability and Lifetime Definitions       | 8   |

|   | Statistical Analysis                                       | 8   |

|   | The Reliability Model for MOS Transistors Based            | 9   |

|   | on Statistical Method                                      | 9   |

|   |                                                            | 10  |

|   | and Lifetime Prediction for PMOS Transistors               | 10  |

|   | PMOS Degradation                                           | 12  |

|   |                                                            | 13  |

|   | Numerical ResultsProposed PMOS Model                       | 13  |

|   | Concluding Remarks for PMOS Modeling.                      | 16  |

|   | Statistical Model of Hot-Carrier Degradation               | 10  |

|   | and Lifetime Prediction for NMOS Transistors               | 18  |

|   | Modeling of Hot Carriers                                   | 18  |

|   | Statistical Methods                                        | 19  |

|   | Numerical Results.                                         | 20  |

|   |                                                            | 20  |

|   | Lifetime Prediction                                        | 22  |

|   | Concluding Remarks for NMOS                                | 25  |

|   | References                                                 | 23  |

| 3 | Demonstration of Proposed Method with Application Examples | 29  |

|   | Basic Concept                                              | 29  |

|   | Hot Carrier Effects                                        | 30  |

|   | Weibull Distribution                                       | 31  |

|   | Experiments and Application Example                        | 32  |

|   | Concluding Remarks.                                        | 39  |

|   | Demonstration on an Application Example of CMOS Inverter   | 39  |

x Contents

|   | Lifetime Prediction                                           | 40 |

|---|---------------------------------------------------------------|----|

|   | Concluding Remarks                                            | 41 |

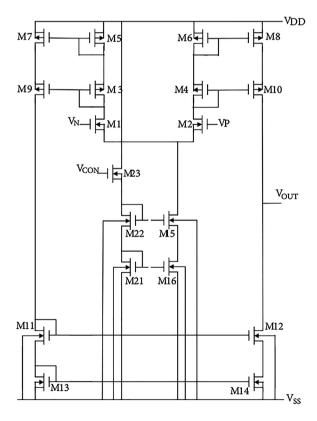

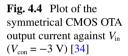

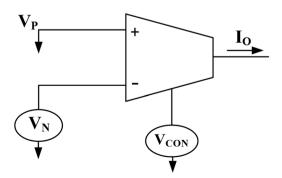

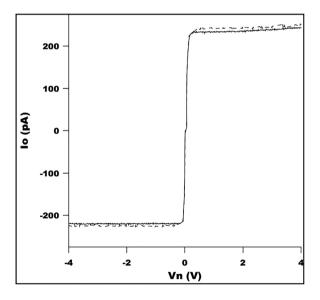

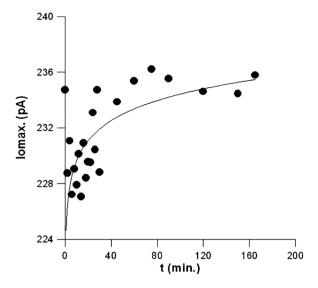

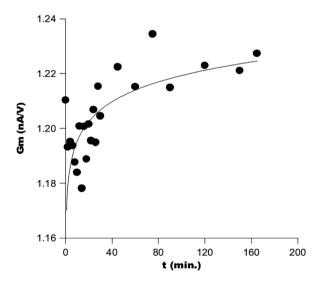

|   | Statistical Investigation of Symmetrical CMOS OTA Degradation | 42 |

|   | Basic Concept                                                 | 42 |

|   | Statistical Method                                            | 43 |

|   | Results                                                       | 44 |

|   | Concluding Remarks                                            | 49 |

|   | References                                                    | 49 |

| 4 | On the Degradation of OTA-C-Based CMOS Low-Power              |    |

|   | Filter Circuits for Biomedical Instrumentation                | 53 |

|   | Basic Concept                                                 | 53 |

|   | Method                                                        | 55 |

|   | Application Example of EEG Filter                             | 59 |

|   | Concluding Remarks                                            | 62 |

|   | On the Reliability of Symmetrical CMOS OTA Operating          |    |

|   | in Subthreshold Region, a Reliability Macromodel              | 62 |

|   | Basic Concept                                                 | 62 |

|   | Measurements                                                  | 63 |

|   | Experimental Results                                          | 64 |

|   | Lifetime Estimation for CMOS OTA                              | 64 |

|   | Concluding Remarks                                            | 68 |

|   | References                                                    | 69 |

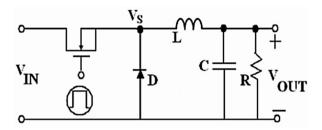

| 5 | Power MOSFET Degradation and Statistical Investigation        |    |

|   | of the Degradation Effect on DC-DC Converters and             |    |

|   | Converter Parameters                                          | 71 |

|   | Basic Concept                                                 | 71 |

|   | Material and Method                                           | 72 |

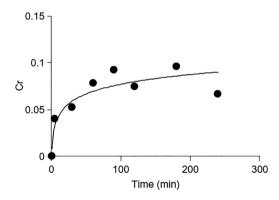

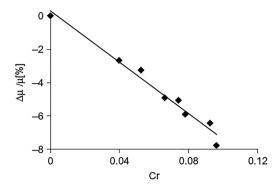

|   | Electrical Stress Effects on CoolMOS Transistors              | 73 |

|   | Channel Length Decrease in CoolMOS Transistors                | 73 |

|   | Mobility Decreasing Coefficient Extraction                    | 74 |

|   | Concluding Remarks                                            | 76 |

|   | Investigation of Degraded Power MOSFET Effects on the         |    |

|   | Performance of DC–DC Converters Using Statistical Methods     | 77 |

|   | Basic Concept                                                 | 77 |

|   | Materials and Method                                          | 77 |

|   | Experimental Results                                          | 80 |

|   | Simulation Results                                            | 81 |

|   | Concluding Remarks                                            | 84 |

|   | High-Voltage Stress Effects on Power MOSFETs                  |    |

|   | in Switching DC–DC Converters                                 | 84 |

|   | Basic Concept                                                 | 84 |

|   | Experiment Platform and Procedure                             | 85 |

|   | Results and Discussion                                        | 85 |

|   | Concluding Remarks.                                           | 90 |

|   | References.                                                   | 90 |

| - | lov                                                           | 03 |

|   |                                                               |    |

# **About the Author**

Hakan Kuntman received his B.Sc., M.Sc., and Ph.D. degrees from Istanbul Technical University in 1974, 1977, and 1982, respectively. In 1974, he joined the Electronics and Communication Engineering Department of Istanbul Technical University. Since 1993, he has been a Professor of electronics in the same department, from which he retired in 2016. His research interest includes the design of electronic circuits, modeling of electron devices and electronic systems, active filters, and the design of analog IC topologies. Dr. Kuntman has authored many publications on modeling and simulation of electron devices and electronic circuits for computer-aided design, analog VLSI design, and active circuit design. He is the author or co-author of 129 journal papers published or accepted for publishing in international journals, 179 conference papers presented or accepted for presentation in international conferences, and 161 Turkish conference papers presented at national conferences. Additionally, he has written 10 books related to the abovementioned areas, with an h-index of 39. He has advised and supervised the completion of the work of 16 Ph.D. and 44 M.Sc. students, Dr. Kuntman is a member of the Chamber of Turkish Electrical Engineers (EMO).

From 2001 to 2004, he served as the Head of the Electronics and Communication Engineering Department, and from 2004 to 2010, he was the Dean of the Electrical and Electronics Engineering Faculty at Istanbul Technical University. Furthermore, Dr. Kuntman is one of the founders of the ELECO conferences and acted as the Conference Chairman several times. His book entitled *Trends in Circuit Design for Analog Signal Processing* was published by Springer in 2022.

**Deniz Özenli** received his B.Sc. degree in Electrical and Electronics Engineering from Istanbul University in 2009 and his M.Sc. and Ph.D. degrees from Istanbul Technical University in 2011 and 2018, respectively. During his Ph.D., he carried out different analog filter applications based on MOSFET-only and MOSFET-C building blocks. He is now an Associate Professor in the Electronics Engineering department of the Turkish Air Force Academy. His main research interests include analog filters, low-voltage current and voltage mode circuits, computer-aided ana-

xii About the Author

log circuit design, VLSI design, as well as image and video processing. He is the author or co-author of approximately 38 scientific papers published in well-esteemed journals and conference proceedings.

Firat Kacar received his B.Sc., M.Sc., and Ph.D. degrees in Electrical and Electronics Engineering from Istanbul University in 1998, 2001, and 2005, respectively. He is currently a Full Professor at the Electrical and Electronics Engineering Department of Istanbul University-Cerrahpasa. His current research interests include analog integrated circuits, RF integrated circuits, active synthetic inductors, analog signal processing circuits, memristors, and electronic device modeling. During his tenure as a faculty member, he has supervised and completed the supervision of 15 Ph.D. and 35 M.Sc. theses. He has worked as a manager or researcher in 30 research projects (ISTKA, TÜBİTAK, and BAP). He is the author or co-author of approximately 200 papers published in scientific journals or conference proceedings. He has been included in the "World's Most Influential Scientists" list published annually by Stanford University and Elsevier for five consecutive years (2019–2023). He achieved great success in this prestigious list, being included in both the annual impact category and the career-long impact category. He currently serves as the chair of the Department of Electrical and Electronics Engineering (since 2018) at Istanbul University-Cerrahpasa.

**Yasin Özçelep** received his B.Sc., M.Sc., and Ph.D. degrees in Electrical and Electronics Engineering from Istanbul University in 2002, 2004, and 2009, respectively. He is currently a Full Professor at the Electrical and Electronics Engineering Department of Istanbul University-Cerrahpasa. His current research interests include semiconductor devices, micro-nano electronics, reliability modelling of semiconductor devices, and hydrogen fuel cells. During his tenure as a faculty member, he has supervised and completed the supervision two Ph.D. and four M.Sc. theses. He has worked as a manager or researcher on 13 research projects. He is the author or co-author of approximately 41 papers published in scientific journals or conference proceedings. He currently serves as the vice-chair of the Department of Electrical and Electronics Engineering at Istanbul University-Cerrahpasa.

# Chapter 1 Introduction

1

The down-scaling of device dimensions in MOS technology will improve performance and packing density for VLSI circuits, but it will negatively affect the quality of the circuits because of reliability problems arising from several physical degradation effects.

Although digital signal processing is becoming increasingly more powerful and many types of signal processing have indeed moved to digital domain due to the advances in IC technology, analog circuits are fundamentally necessary in many complex and high performance systems. This is caused by the reality that naturally occurring signals are analog. In other words, analog circuits act as a bridge between the real world and digital systems. In analog signal processing, many circuit topologies including active filters, oscillators, immittance simulators, etc. have been proposed in the literature [1–22].

Application area of analog signal processing is wide and ranges from very low frequencies at several Hertz levels to RF applications operating at gigahertz level, that means, from biomedical and sonar signals to cognitive radio and encrypted communications [1, 2, 11, 12, 14–17, 20–22].

Today, modern CMOS technologies are continuously scaling down; but as a result of this, analog designers have serious reliability problems in their designs caused by physical effects such as

- Hot-carrier injection,

- negative and positive bias temperature instability (N/PBTI),

- time-dependent dielectric breakdown (TDDB) [23–58].

Therefore, it is an important factor estimating the deviations caused by these degradation mechanisms to obtain a robust design. Note that the reliability of CMOS structures are considered for more than 40 years [58–64]. The subject is still popular and several new publications are available in the literature [49–54, 63].

The reliability of a system is defined as the probability that it will perform its required function under stated conditions for a stated period of time.

2 1 Introduction

In most reliability studies on the modeling of the hot-carrier effect available in the literature, models based on physical properties have been proposed [23–31, 49–54]; however, difficulties in preparation of physical models, losing the actuality within the advances in the technology, and excessively long simulation times seem to be disadvantages of these models.

To overcome these disadvantages of physical models, statistical methods based on the observation results, independent of the technology, and exhibit a short simulation time and high accuracy has been introduced in our work.

The use of statistical approach for reliable and optimal design of systems, including electronic systems, has become quite popular. Statistically designed experiments/simulations have been used extensively for estimating or demonstrating existing reliability by identifying the important parameters (factors) affecting reliability out of many potentially important ones [1, 2]. This statistical approach ensures the performance and safety of critical electronic systems employed for space, nuclear, automotive, weapons, sub-marine and aerospace applications, to name a few [60, 61, 64]. A statistical life model becomes more reliable, valuable, and useful, if it fits the experimental data quite well.

Starting with experimental results of Siemens AG., Munich, Germany [35] and TUBITAK (Turkish Research and Technological Council), the effect of hot carriers on the drain current and threshold voltage of PMOS and NMOS transistors was statistically investigated and a statistical model was proposed as an alternative to those available in the literature [32–34, 43–48].

This book gives a review of our previously performed works on statistical method based modeling of the degradation in the drain current and threshold voltage of the NMOS and PMOS transistors. All of the works were performed by our research group in the frame of Ph.D. and M.Sc. Thesis works in Istanbul University and Istanbul Technical University [32–34, 43–48]. Note that these models are based on the observations by operating the device under stress voltage conditions.

For this purpose, measurements are performed on test transistors fabricated with the same technology but with different channel lengths. In other words, to specify the model, test transistors with different dimensions are necessary. Note that these measurements and observations are also needed for physical modeling, but complex equations must be derived for this purpose and implemented into circuit simulators which appear as an important disadvantage [35, 36].

The time-dependent statements of degradation were obtained by using different statistical methods. Coefficients were optimized with these methods and functions were generated. These functions gave variations of drain current with time and channel length. The observed and the estimated values of the degradation are compared.

The structure of the book is as follows: The Introduction Section, Chap. 1, describing the basic concept is followed by Chap. 2 reflecting the definition of reliability analysis and statistical methods. The reliability model for PMOS and NMOS transistors based on statistical methods are given in this section. Demonstration on interesting application examples are given in Chap. 3 which reflects the behavior of a current source-loaded single stage amplifier, CMOS inverter and CMOS OTA. The

References 3

following part, Chap. 4, describes in detail the behavior of a CMOS OTA operating in subthreshold region which is also demonstrated with measurement results. Two different methods are given in this chapter. In addition, a CMOS degradation macromodel is also introduced in this section. Finally, Chap. 5 describes the reliability of power MOSFET circuits demonstrated by giving example circuits.

We think that this book will be useful for analog circuit designer working in the related area and provides a simple and useful alternative to physical methods available in the literature.

### References

- Y. Lakys, A. Fabre, Multistandard transceivers: state of the art and a new versatile implementation for fully active frequency agile filters. Analog Integr. Circ. Sig. Process 74(1), 63–78 (2013)

- Y. Lakys, B. Godara, A. Fabre, Cognitive and encrypted communications: state of the art and a new approach for frequency-agile filters. Turk. J. Electr. Eng. Comput. Sci. 19(2), 251–273 (2011)

- 3. X. Li, M. Ismail, A single-chip CMOS front-end receiver architecture for multi-standard wireless applications, in *Proc. ISCAS 2001. The 2001 IEEE International Symposium on Circuits and Systems* (2001)

- 4. F. Kacar, H. Kuntman, A new improved CMOS realization of CDTA and its filter application. TJEECS Turk. J. Electr. Eng. Comput. Sci. 19, 631–642 (2011)

- E. Armağan, H. Kuntman, Configurable frequency agile filter application of balanced differential pair based CCCII circuit in 28nm process, in *Proc. LASCAS 2013: IEEE Fourth Latin American Symposium on Circuits and Systems* (2013)

- E. Alaybeyoğlu, H. Kuntman, A new frequency agile filter structure employing CDTA for positioning systems and secure communications. Analog Integr. Circ. Sig. Process 89(3), 693–703 (2016)

- E. Arslan et al., MOS-only second order current-mode LP/BP filter. Analog Integr. Circ. Sig. Process 74(1), 105–109 (2013)

- 8. Y. Lakys et al., Cognitive and encrypted communications, part 2: a new approach to active frequency-agile filters and validation results for an agile bandpass topology in SiGe-BiCMOS, in *Proc. ELECO 2009: International Conference on Electrical and Electronics Engineering*, Bursa, Turkey (2009)

- 9. D. Biolek et al., Active elements for analog signal processing: classification, review, and new proposals. Radioengineering 17(4), 15–32 (2008)

- M. Altun, H. Kuntman, Design of a fully differential current mode operational amplifier with improved input—output impedances and its filter applications. AEU-Int. J. Electron. Commun. 62(3), 239–244 (2008)

- 11. E. Alaybeyoğlu, H. Kuntman, CMOS implementations of VDTA based frequency agile filters for encrypted communications. Analog Integr. Circ. Sig. Process **89**(3), 675–684 (2016)

- K. Soon-Jae et al., Reconfigurable high-order moving-average filter using inverter-based variable transconductance amplifiers. IEEE Trans. Circuits Syst. II Exp. Briefs 61(12), 942–946 (2014)

- E. Alaybeyoğlu, New Possibilities in the Design of CMOS Frequency Agile Filters.

Ph.D. Thesis, İstanbul Technical University, Graduate School of Science Engineering and Technology, July 2017

- 14. H. Kuntman, New trends in circuit design for analog signal processing (Invited paper for IEEE special session on circuits and systems (CAS) education—history and future prospects-1),

4 1 Introduction

- in *Proc. of ELECO 2011: The 7th International Conference on Electrical and Electronics Engineering*, Bursa, Turkey, 1–4 December 2011, pp. 18–25

- 15. H. Kuntman, On the modeling of electron devices: concept, accuracy criterion with application examples, importance in EE education. (Invited paper for IEEE special session on circuits and systems (CAS) education—history and future prospects-1), in *Proc. of ELECO 2013: The 8th International Conference on Electrical and Electronics Engineering*, Bursa, Turkey, 28–30 November 2013, pp. 1271–1278

- E. Alaybeyoğlu, H. Kuntman, New realization methods of frequency agile filters for encrypted communications and multi-standard transceivers (Invited Talk), in *Proc. of ICTUS'2017: International Conference on Infocom Technologies and Unmanned Systems*, Amity University, Dubai, 18–20 December 2017, pp. 99–112

- T.-Y. Lo, C.-C. Hung, M. Ismail, A wide tuning range G<sub>m</sub>-C filter for multi-mode CMOS direct-conversion wireless receivers. IEEE J. Solid State Circuits 44(9), 2515–2524 (2009)

- H. Kuntman, A. Zeki, Novel approach to the calculation of non-linear harmonic distortion coefficients in CMOS amplifiers. Microelectron. J. 29(1–2), 43–48 (1998)

- 19. A. Zeki, H. Kuntman, New MOSFET model suitable for analogue IC analysis. Int. J. Electron. **78**(2), 247–260 (1995)

- G. Düzenli, Y. Kılıç, H. Kuntman, A. Ataman, On the design of low-frequency filters using CMOS OTAs operating in the subthreshold region. Microelectron. J. 30(1), 45–54 (1999)

- 21. A. Uygur, H. Kuntman, DTMOS-based 0.4V ultra low-voltage low-power VDTA design and its application to EEG data processing. Radioengineering 22(2), 458–466 (2013)

- A. Uygur, H. Kuntman, A very compact, 0.4V DTMOS CCII employed in an audio-frequency filter. Analog Integr. Circ. Sig. Process 81(1), 89–98 (2014)

- 23. Mitsubishi Electric Co., Failure Mechanism of Semiconductor Devices, pp. 11-15

- 24. A. Bravaix, D. Gougenhim, N. Revil, M. Varrot, P. Mortini, *Effects of High Temperature on Performances and Hot-Carrier Reliability in DC/AC Stressed 0.35μm n-MOSFET's*. Electronic Industries Association Publication. www.iea.org

- R. Thewes, M. Brox, G. Tempel, K. Goser, Channel-length-independent hot carrier degradation in analog p-MOS operation. IEEE Electron Device Lett. 13(11), 590–592 (1992)

- W. Weber, M. Brox, A.V. Schwerin, R. Thewes, Hot carrier stress effects in p-MOSFETs: physical effects relevant for circuit operation. Microelectron. Eng. 22(1–4), 253–260 (1993)

- Y. Pan, A physical-based analytical model for the hot carrier induced saturation current degradation of p-MOSFETs. IEEE Trans. Electron Devices 41(1), 84–89 (1994)

- R. Thewes, W. Weber, Effects of hot carrier degradation in analog CMOS circuits. Microelectron. Eng. 36, 285–292 (1997)

- 29. W. Weber, Dynamic stress experiments for understanding hot-carrier degradation phenomena. IEEE Trans. Electron Devices **35**(9), 1476–1486 (1988)

- 30. E. Li, S. Prasad, Channel width dependence of NMOSFET hot-carrier degradation. IEEE Trans. Electron Devices **50**(6), 1545–1547 (2003)

- Y. Wang, Y. Zhao, B.M. Khan, C.L. Doherty, J.D. Krayer, M.H. White, A novel SONOS nonvolatile flash memory device using substrate hot-hole injection for write and gate tunneling for erase. Solid State Electron. 48, 2031–2034 (2004)

- 32. F. Kaçar, New Approaches for the Modelling of Hot Carrier Effect in MOSFET's. Ph.D. Thesis, Institute of Sciences, Istanbul University (2005)

- 33. F. Kaçar, A. Kuntman, H. Kuntman, A simple approach for modelling the infulence of hotcarrier effect on threshold voltage of MOS transistors, in *Proc. of the 13th International Conference on Microelectronics (ICM'2001)*, Rabat, Morocco (2000), pp. 43–46

- 34. A. Kuntman, A. Ardalı, H. Kuntman, F. Kaçar, A Weibull distribution-based new approach to represent hot carrier degradation in threshold voltage of MOS transistors. Solid State Electron. **48**(2), 217–223 (2004)

- 35. G. Düzenli, Development of MOSFET Models Suitable for Simulation of Analog CMOS Circuits After Hot-Carrier Stress. Ph.D. Thesis, supported by ITU-ETA Foundation, Siemens

- Türk A.Ş. İstanbul Turkey and Siemens AG München/Germany under research number MW-/ Kuntman\_J303.0, Istanbul Technical University, Institute of Science and Technology (2003)

- 36. G. Düzenli, H. Kuntman, The basic of an analytical model development for the P-MOS transistor degradation, in *Proc. of OPTIM'2002 (8th International Conference: Optimization of Electrical and Electronic Equipment)*, Brasov, Romania, 16–17 May 2002, pp. 829–834

- S. Minehane, P. O'Sullivan, A. Mathewson, B. Mason, Evolution of BSIM3v3 parameters during hot-carriers stress, in 1997 IEEE International Integrated Reliability Workshop Final Report (Cat. No.97TH8319), Lake Tahoe, CA, USA (1997), pp. 110–118. https://doi. org/10.1109/IRWS.1997.660297

- 38. S. Minehane, S. Healy, P. O'Sullivan, K. McCarty, A. Mathewson, B. Mason, Direct BSIM3v3 parameter extraction of n-channel LDD MOSFETs. *IEEE IRW Final Report* (1997), pp. 110–118

- 39. H. Wong, M.C. Poon, Simulation of hot-carriers reliability in MOS integrated circuits, in *Proc. ICM* '97 (1997), pp. 625–628

- K.N. Quader, C.C. Li, R. Tu, E. Rosenbaum, P.K. Ko, C. Hu, A bidirectional NMOSFET current reduction model for simulation of hot-carrier circuit degradation. IEEE Trans. Electron Devices 40(12), 2245–2254 (1993)

- 41. G. Groseneken, Hot carrier degradation and ESD in submicron CMOS technologies: how do they interact? IEEE Trans. Device Mater. Reliab. 1, 23–32 (2001)

- 42. Y.S. Jean, C.Y. Wu, The threshold-voltage model of MOSFET device with localized interface charge. IEEE Trans. Electron Device **44**, 441–447 (1997)

- F. Kaçar, A. Kuntman, H. Kuntman, Statistical model of hot-carrier degradation and lifetime prediction for P-MOS transistors. Turk. J. Electr. Eng. Comput. Sci. (ELEKTRIK) 14(3), 417–428 (2006)

- 44. Y. Özcelep, A. Kuntman, H. Kuntman, Statistical investigation of symmetrical CMOS OTA degradation. J. Electr. Electron. Eng. Eng. Faculty Istanbul Univ. 8(1), 549–555 (2008)

- Y. Özcelep, A. Kuntman, H. Kuntman, On the degradation of OTA-C based CMOS low-power filter circuits for biomedical instrumentation. TJEECS Turk. J. Electr. Eng. Comput. Sci. 20(Suppl. 2), 1359–1368 (2012)

- 46. F. Kaçar, A. Kuntman, H. Kuntman, Statistical investigation of hot-carrier degradation and lifetime prediction of PMOS transistors, in *Proc. of ELECO 2005: The 4th International Conference on Electrical and Electronics Engineering, (Electronics)*, Bursa, Turkey, 7–11 December 2005, pp. 76–80

- 47. F. Kaçar, A. Kuntman, H. Kuntman, A new approach of hot-carrier degradation and lifetime prediction for N-MOS transistors, in *Proc. of MELECON'06: The 13th IEEE Mediterranean Electrotechnical Conference*, Benalmádena, Málaga, Spain, 16–19 May 2006, pp. 129–132

- 48. Y. Özcelep, Mos Tranzistörlerde Hızlı Yaşlandırma ile Güvenilirlik Koşullarının Belirlenmesi. M.Sc. Thesis, Institute of Sciences, Istanbul University (2006)

- 49. M.T. Sanic, M.B. Yelten, Impact of transistor scaling on the time-dependent dielectric breakdown (TDDB) reliability of analog circuits, in *Proc. of ELECO 2017: The 10th International Conference on Electrical and Electronics Engineering*, Bursa, Turkey, 30 November–2 December 2017, pp. 476–480

- E. Afacan, M.B. Yelten, G. Dündar, Review: analog design methodologies for reliability in nanoscale CMOS circuits, in *Proc. of 14th International Conference on Synthesis, Modeling,* Analysis and Simulation Methods and Simulation Methods and Applications to Circuit Design, SMACD2017 (2017)

- M.B. Yelten, P.D. Franzon, M.B. Steer, Surrogate-model-based analysis of analog circuits part II: reliability analysis. IEEE Trans. Device Mater. Reliab. 11(3), 466–473 (2011). https://doi.org/10.1109/TDMR.2011.2160063

- E. Maricau, G. Gielen, Computer-aided analog circuit design for reliability in nanometer CMOS. IEEE Trans. Emerg. Sel. Top. Circuits Syst. 1(1), 50–58 (2011)

6 1 Introduction

53. G. Gielen, E. Maricau, P. De Wit, Analog circuit reliability in Sub-32 nanometer CMOS: analysis and mitigation, in *Proc. of Conference: Design, Automation and Test in Europe, DATE 2011*, Grenoble, France, 14–18 March 2011

- N. Heidmann, N. Hellwege, S. Paul, D. Peters-Drolshagen, NBTI and HCD aware behavioral models for reliability analysis of analog CMOS circuits, in *IEEE IRPS*, Monterey, USA, April 2015

- R.D. Kulkarni, V. Agarwal, Taguchi based performance and reliability improvement of an ion chamber amplifier for enhanced nuclear reactor safety. IEEE Trans. Nucl. Sci. 55(4), 2303–2314 (2008)

- 56. C.K. Chen et al., Optimal design of DC-DC converter with LC snubber by hybrid method, in Proc. of the 3rd International Conference on Innovative Computing Information and Control (ICICIC'08) (2008), pp. 166–169

- 57. P.J. Ross, Taguchi Techniques for Quality Engineering (McGraw-Hill, New York, 1988)

- 58. G.L. Schnable, L.J. Gallace, H.L. Pujol, Reliability of CMOS integrated circuits. IEEE Comput. **11**(10), 6–17 (1978)

- 59. Y. Özcelep, A. Kuntman, H. Kuntman, On the reliability of symmetrical CMOS OTA operating in subthreshold region, in *Proc of MELECON'06: The 13th IEEE Mediterranean Electrotechnical Conference*, Benalmádena, Málaga, Spain, 16–19 May 2006, pp. 191–194

- 60. A. Kuntman, H. Kuntman, Circuit model for statistical method based reliability estimation of MOS transistors and analog CMOS circuits (Invited Talk), in *Proc. of ICRITO'2018: International Conference on Reliability, Infocom Technologies and Optimization*, Amity University Uttar Pradesh, Noida, India, 29–31 August 2018, pp. 97–107

- 61. A. Kuntman, H. Kuntman, On the reliability estimation of analog CMOS circuits based on statistical methods (Invited Talk), in *Proc. of ELECO'2019: 11th International Conference on Electrical and Electronics Engineering*, EMO, Bursa, Turkey, 28–30 November 2019

- 62. A. Kuntman, H.H. Kuntman, Statistical methods based reliability estimation for MOS transistors and analog CMOS circuits (Invited Talk), in *Proc. of ELECO'2022: 13th International Conference on Electrical and Electronics Engineering*, EMO, Bursa, Turkey, 24–26 November 2022

- 63. H. Kuntman, D. Özenli, *Trends in Circuit Design for Analog Signal Processing* (Springer, Cham, 2022)

- 64. M. Ugur, A. Kuntman, A. Merev, Investigation of the ageing process in polymeric insulators by using improved Weibull statistics, in *The 2002 IEEE International Symposium on Electrical Insulation*, Boston, MA, 7–10 April 2002

# Chapter 2 The Reliability Model for PMOS and NMOS Transistors Based on Statistical Methods

# **Basic Concepts: Reliability and Lifetime Definitions**

The use of statistical approach for reliable and optimal design of systems, including electronic systems, has become quite popular [1–42]. Statistically designed experiments/simulations have been used extensively for estimating or demonstrating existing reliability by identifying the important parameters (factors) affecting reliability out of many potentially important ones [1, 2]. This statistical approach ensures the performance and safety of critical electronic systems employed for space, nuclear, automotive, weapons, sub-marine, and aerospace applications, to name a few [40–42]. A statistical life model becomes more reliable, valuable and useful, if it fits the experimental data quite well.

In this section, we begin with the definition of the basic concept of reliability and lifetime estimation concepts. The reliability of a system is defined as the probability that it will perform its required function under stated conditions for a stated period of time.

In most reliability studies on the modeling of the hot-carrier effect available in the literature, models based on physical properties have been proposed [1–8, 27–32]; however, difficulties in the preparation of physical models, losing the actuality within the advances in the technology, and excessively long simulation times seem to be disadvantages of these models.

In order to allow a prediction of device lifetime in real life, stress levels from results obtained under actual stress conditions must be used. With such results, empirical models for hot-carrier degradation and several extrapolation laws to calculate the lifetime have been developed. However, the proposed model combines a hot-carrier degradation model and lifetime prediction model into a single model [3–7]. Lifetime predictions for MOS transistors have been performed using the criteria given in the literature [3]. They can reach 10% of the lifetime criteria [3] for hot carriers in DC stress applications in 10 years or less.

**Table 2.1** Obtained functions of the investigated methods [3]

| Power method        | $F(t) = a \cdot t^b$                   |

|---------------------|----------------------------------------|

| Power-log-I method  | $F(t) = a \cdot \ln(t)^b$              |

| Power-log-II method | $F(t) = a \cdot t^b \cdot \ln(t)$      |

| Weibull method      | $F(t) = 1 - \exp\left[-(t/a)^b\right]$ |

Table 2.1 tabulates obtained functions of the investigated methods where for all methods t = time, a = scale parameter, b = shape parameter. Calculations are based on linear regression method for the four approaches and least squares methods have been used [10, 21, 24, 25]. So, calculations were performed by using MATLAB program.

# **Statistical Analysis**

Life models establish a relationship between applied stresses and failure time. They provide useful parameters for material characterization and comparison [6]. Several authors proposed probabilistic life models for insulating materials subjected to electrical and thermal stresses. In general, these models are derived from two basic approaches. One model is based on the study of degradation breakdown mechanisms and provides as a final product a relationship between applied stresses and time to breakdown. The other model deals with the phenomenological observations of the results of life tests and tries to fit these results to appropriate models. In both cases, however, the problem to individualize the behavior of an insulating material subjected to selected stresses, based on the results of life tests, is quite difficult due to the hidden technological features, such as curing technique, test cell, test methods, and other factors [7]. A statistical life model becomes more reliable, valuable, and useful, if it fits the experimental data quite well.

Since the 1970s, the Weibull probability distribution has gained wide acceptance in the statistical treatment of the time to electrical breakdown of solid dielectrics. It affords an excellent approximation to the probability law of many random variables. Many methods, such as "maximum likelihood," "linear estimation" or "graphical plotting technique," have been developed to estimate the parameters. "Maximum likelihood technique" is the best method among them, because it can be used for any number of test specimens and can estimate the parameters quite accurately. "Linear estimation" methods are also quite accurate; however, they require extensive tables of factors for each sample size [8, 9, 15].

The "graphic plotting technique" has the disadvantage in being an observer. The data is dependent method which can lead to some inaccuracies in data statistically. However, this method is selected here because it is simple, quite easy to implement and can quickly check the validity of the Weibull distribution in representing the data [9].

# The Reliability Model for MOS Transistors Based on Statistical Method

For more than 20 years, continuous scaling of CMOS devices to smaller dimensions has resulted higher devices density, faster circuit speed, and lower power dissipation. Currently, CMOS technologies less than 0.1 µm are widely used in the manufacturing of integrated circuit, several publications on analog CMOS structure and on the reliability of them are available in the literature [1–42]. Many new physical effects become significant as the device size shrinks. Examples are the drain induced barrier lowering (DIBL) [4], channel length modulation (CLM) [5], and hot-carrier effects [6–9].

Several works were performed to model the effect of hot carriers [1–42]. Some of these works are based on physical parameters [8] and the other works are focused on determination of behavior characteristics with physical quantities [6]. Both of two models are complex and take a long computational time. Parameters are characterized with respect to observation result in our studies [10, 11]. To overcome these disadvantages of the physical models, a statistical method that is based on the observation results, independent from the technology and exhibits short simulation times and high accuracy has been introduced in this work. Starting from experimental results of Siemens AG., Muenchen, Germany [13, 14], the effect of hot carriers on the drain current and threshold voltage of NMOS transistors were investigated statistically and a statistical model was proposed to be an alternative to those available in the literature. The time-dependent equations of degradation were obtained by using four different statistical methods. Due to dependence on time and channel length of obtained functions and expressions for different channel lengths with unique function supply facility in working for users obtained results can be applied to all transistors that are proposed with same process. The use of statistical approach for reliable and optimal design of systems, including electronic systems, has become quite popular. Statistically designed experiments/simulations have been used extensively for estimating or demonstrating existing reliability by identifying the important parameters (factors) affecting reliability out of many potentially important ones. This statistical approach ensures the performance and safety of critical electronic systems employed for space, nuclear, automotive, weapons, sub-marine, and aerospace applications, to name a few.

In this section, degradation models for NMOS and PMOS transistors based on statistical methods will be described. The study was performed for three different transistors produced with the same technology, but with different channel lengths [10, 21, 24, 25, 40–42]. Calculations are based on linear regression method for the four approaches and least squares methods have been used [10, 21, 24, 25]. So, calculations were performed by using MATLAB program.

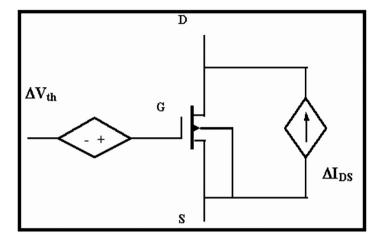

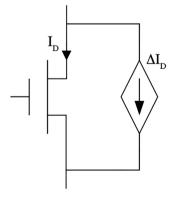

It is apparent from experimental results on test transistors that the drain current and the threshold voltage of NMOS transistors decrease with time. On the other hand, experimental results also show that the drain current and the threshold voltage of PMOS transistors increases with time. The changes in the threshold voltage and

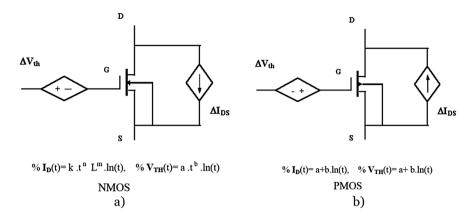

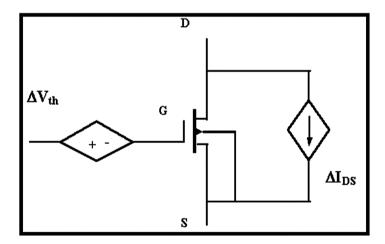

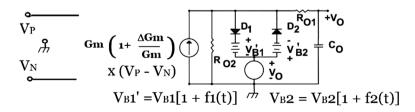

Fig. 2.1 Degradation models for NMOS and PMOS transistors [21]

in the drain current are represented by connecting a time-dependent voltage source series to the gate and a time-dependent current source parallel to drain-source terminals. According to the observed device behavior, these sources are filled with adequate statistical expressions. The related reliability models for NMOS and PMOS transistors are illustrated in Fig. 2.1a, b.

In this section, we describe the related reliability models for PMOS and NMOS transistors in detail using experimental data to demonstrate the accuracy of the method. In the first part, the statistical model for PMOS transistors is given. Second part describes the statistical model for NMOS transistors. Note that there are different mechanisms causing the degradation in PMOS and NMOS transistors.

# Statistical Model of Hot-Carrier Degradation and Lifetime Prediction for PMOS Transistors

The down-scaling of device dimensions in MOS technology will improve performance and packing density for VLSI circuits, but will negatively affect the quality of the circuits. Basically, integrated circuits are classified according to the electrical function they perform. The concept of quality is used to express how well the required function is performed. Several works have been conducted on hot-carrier effect, which is one of the most important factors that influence the reliability of MOS structures [1–13]. The reliability of a system is defined as the probability that it will perform its required function under stated conditions for a stated period of time. In most reliability studies on the modeling of the hot-carrier effect available in the literature, models based on physical properties have been proposed [1–8, 13]; however, difficulties in preparation of physical models, losing the actuality within the advances in the technology, and excessively long simulation times seem to be disadvantages of these models.

PMOS Degradation 11

To overcome these disadvantages of physical models, a statistical method that is based on the observation results, independent of the technology, and that exhibits a short simulation time and high accuracy has been introduced in this work. Starting with experimental results of Siemens AG., Munich, Germany [13], the effect of hot carriers on the drain current and threshold voltage of PMOS transistors was statistically investigated and a statistical model was proposed as an alternative to those available in the literature. The time-dependent statements of degradation were obtained by using three different statistical methods. Coefficients were optimized with these methods and functions were generated. These functions gave variations of drain current with time and channel length. The proposed method is based on the measurement results, is independent of the technology, and can be easily applied to PMOS transistors with different dimensions.

# **PMOS Degradation**

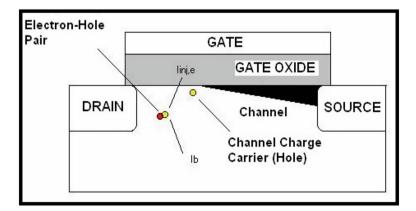

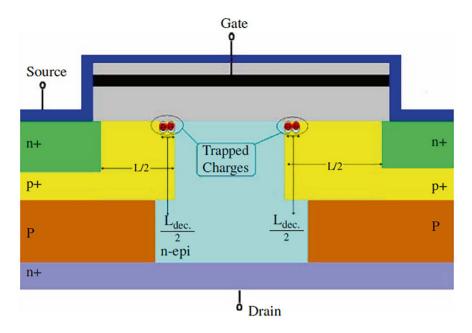

PMOS degradation occurs only if electrons are trapped in the gate oxide due to the impact ionization of hot-holes [1–9]. This is known as the drain avalanche hot-carrier mechanism and is shown in Fig. 2.2. When the PMOS transistor is operating in the saturation region, holes move from the source to the drain and are accelerated by the high electric field at the drain end of the channel. If a hole has energy of at least 1.5 eV, then it can be concluded with impact ionization. After impact ionization, the rise of the new hole moves to the drain, as do the other holes, and it increases the drain current ( $I_D$ ) a small amount. Most of the new electrons, after impact ionization, move to the substrate, forming the substrate current ( $I_B$ ). Nevertheless, some of these electrons, if they have an energy at least of 3.1 eV and the right direction, they surmount the Si–SiO<sub>2</sub> potential barrier and are injected into the gate oxide. The electric field strength direction in the gate oxide above the depletion region causes

Fig. 2.2 Hot-carrier formation mechanism of PMOS transistors [21]

the electron to accelerate to the gate. Most of the electrons in the gate oxide reach the gate from the gate current  $(I_G)$ , which corresponds greatly with the drain current  $(I_D)$ . Yet, the existing traps in the oxide can capture some of the electrons, and these captured electrons behave like fixed negative charges. Electrons that are injected into the gate oxide can damage the  $Si-SiO_2$  interface. These interface defects are partially filled by the holes in the non-saturation operation. Therefore, this degradation effect on a MOSFET will be ignored. The fixed negative charges of the captured electrons cause an increase in the drain current in all regions of operation; however, the largest degradation will be in the saturation operation. For short channel MOSFETs, the threshold voltage  $(V_{th})$  will also change to lower values.

### Statistical Methods

This study was performed for three different transistors produced with the same technology but with different channel lengths. Process parameters of the transistors are given as:  $t_{ox} = 20$  nm and  $x_j = 400$  nm; the dimensions are W = 10  $\mu$ m and L = 1.5  $\mu$ m, 2  $\mu$ m, and 3  $\mu$ m. Stress voltage was applied to the transistors for 16 h. Statistical methods were applied and investigated using variations of the drain currents and threshold voltages with time, which were obtained as a result of applied stress voltages ( $V_D = 0.5$  V,  $V_D = 2.5$  V,  $V_G = 1.5$  V,  $V_G = 2$  V, and  $V_G = 2.5$  V). The investigated methods for PMOS transistors are:

- power method,

- Weibull method,

- logarithmic method.

Calculations were based on the linear regression method for all three approaches and the least squares method was used [21–25, 39]. Exponential and logarithmic parameters and power distribution with the least squares method are given by the following equations. Calculations were performed using the MATLAB program.

In this respect, exponential distribution with the least squares method is given as:

$$y = Ae^{Bx} (2.1a)$$

$$a = \frac{\sum_{i=1}^{n} \ln y_i \sum_{i=1}^{n} x_i^2 - \sum_{i=1}^{n} x_i \sum_{i=1}^{n} (x_i \ln y_i)}{n \sum_{i=1}^{n} x_i^2 - \left(\sum_{i=1}^{n} x_i\right)^2}$$

(2.1b)

$$b = \frac{n\sum_{i=1}^{n} x_{i} \ln y_{i} - \sum_{i=1}^{n} x_{i} \sum_{i=1}^{n} \ln y_{i}}{n\sum_{i=1}^{n} x_{i}^{2} - \left(\sum_{i=1}^{n} x_{i}\right)^{2}}$$

(2.1c)

PMOS Degradation 13

where  $B \equiv b$  and  $A \equiv \exp(a)$ .

Logarithmic Distribution with the Least Squares Method is described as follows:

$$y = a + b \ln(x) \tag{2.2a}$$

$$a = \frac{\sum_{i=1}^{n} y_i - b \sum_{i=1}^{n} \ln x_i}{n}$$

(2.2b)

$$b = \frac{n\sum_{i=1}^{n} (y_i \ln x_i) - \sum_{i=1}^{n} y_i \sum_{i=1}^{n} \ln x_i}{n\sum_{i=1}^{n} (\ln x_i)^2 - \left(\sum_{i=1}^{n} \ln x_i\right)^2}$$

(2.2c)

Power Distribution with the Least Squares Method is given as:

$$y = Ae^{Bx} (2.3a)$$

$$a = \frac{\sum_{i=1}^{n} y_i - b \sum_{i=1}^{n} \ln x_i}{n}$$

(2.3b)

$$b = \frac{n\sum_{i=1}^{n} (\ln y_i \ln x_i) - \sum_{i=1}^{n} \ln x_i \sum_{i=1}^{n} \ln y_i}{n\sum_{i=1}^{n} (\ln x_i)^2 - \left(\sum_{i=1}^{n} \ln x_i\right)^2}$$

(2.3c)

where  $B \equiv b$  and  $A \equiv \exp(a)$ .

### Numerical Results

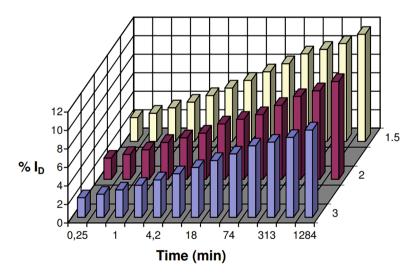

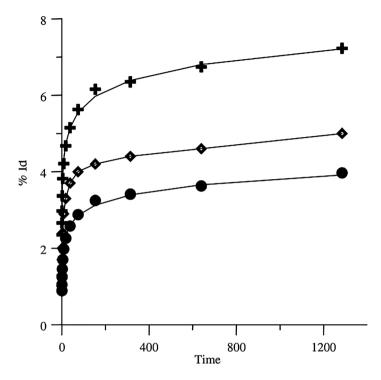

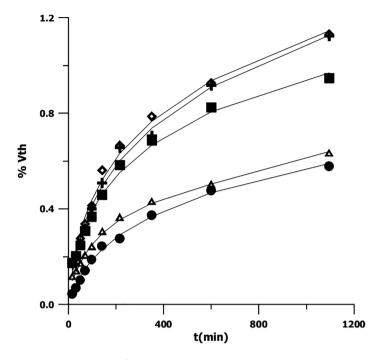

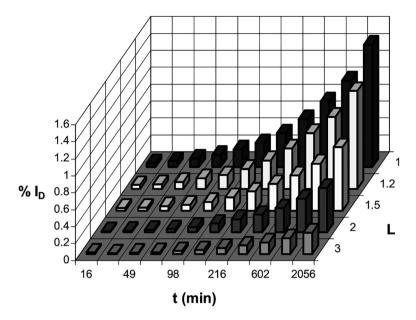

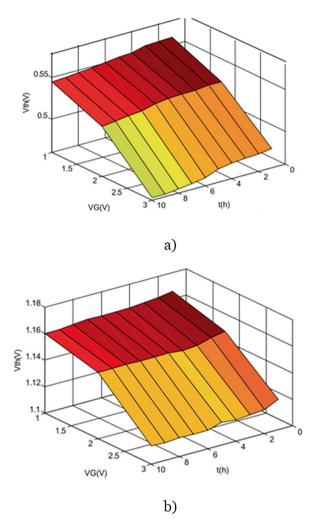

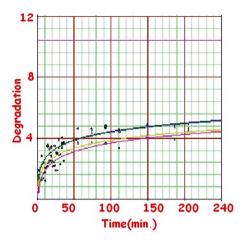

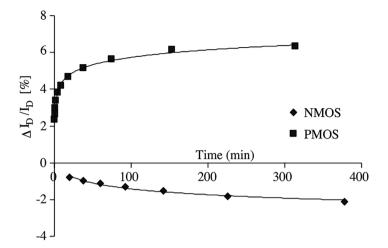

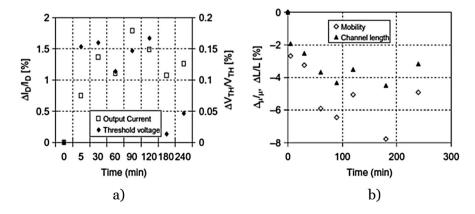

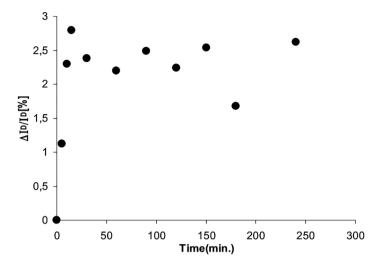

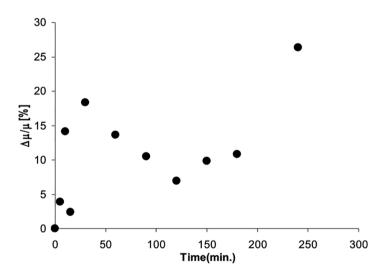

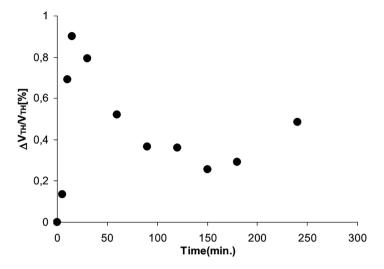

Experimental results for PMOS transistors at different stress conditions are summarized in the 3-dimensional plots of  $I_D = I_D$  (L,t) shown in Fig. 2.3. As can be observed from Fig. 2.3, drain current increases with stress time and  $I_D$  decreases with channel length. On the other hand, based on a previous study [12], it can be easily observed that the drain current and the threshold voltage of NMOS transistors decrease with time. For  $L = 1.5 \, \mu m$ , the change in the drain current is approximately 4% for PMOS, while it is 0.8% for NMOS. It seems that PMOS transistors are more affected by hot carriers. The power, logarithmic, and Weibull parameters were calculated using experimental data and the linear regression method, including Equations. The functions obtained by using the investigated methods that gave the percentage changes in drain currents and threshold voltages are given in Table 2.2. Coefficients were optimized with these methods and functions were generated.

These functions gave variation of drain current with time and channel length. The function coefficients for different operating conditions obtained by the three methods can be seen in Table 2.3.

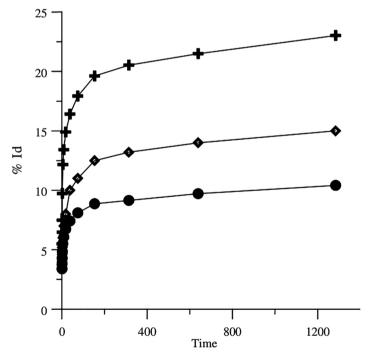

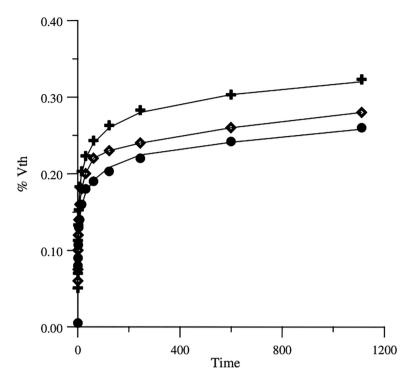

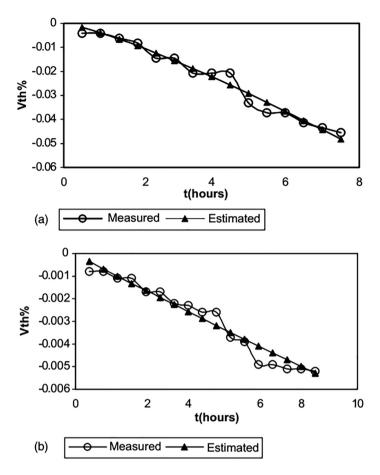

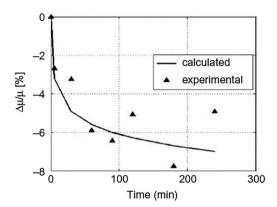

The results calculated from the equations given in Table 2.1 are compared with experimental results. It has been observed that the logarithmic method seems to be the best statistical method that characterizes the measurement results. The characterization results using the logarithmic method are given with experimental results shown in Figs. 2.4, 2.5, and 2.6.

It seems from the figures that there is good agreement between the experimental results and the calculated values. To show the similarity between the measured and calculated values, correlation coefficients were calculated and very highly correlated coefficients were obtained. The results obtained can be seen in Table 2.4. Moreover, error calculations were achieved with the RMS method and the results are given in Table 2.5. It can easily be observed that the error values are very low. With respect to the graphics, the table of correlation coefficients, and the table of RMS errors, the methods are classified from the best to worst as the logarithmic, power, and Weibull methods, respectively.

# **Proposed PMOS Model**

It is clearly seen that the drain current and the threshold voltage of the PMOS transistor increase with time. An appropriate model was designed to represent the hot-carrier effect of the transistors in this work. With the help of the obtained

Fig. 2.3 Experimentally determined dependence of the drain current on channel length and stress time [21]

PMOS Degradation 15

**Table 2.2** Obtained functions of the investigated methods [21]

| Investigation method | Obtained function                                   |  |

|----------------------|-----------------------------------------------------|--|

| Power                | $\%I_{\mathrm{D}}(t,L) = k \cdot L^{m} \cdot t^{n}$ |  |

| Logarithmic          | $\%I_{\mathrm{D}}(t,L) = k \cdot L^{m} + n \ln(t)$  |  |

| Weibull              | $%I_{D}(t,L) = 1 - \exp(-(t/k \cdot L^{m}))^{n}$    |  |

Table 2.3 Obtained function coefficients of PMOS transistors for different methods [21]

|                                       | Power      | Logarithmic | Weibull    |

|---------------------------------------|------------|-------------|------------|

| $I_{\rm D}(V_{\rm D}=0.5\rm V)$       | k = 3.158  | k = 3.036   | k = 270    |

|                                       | m = -1.175 | m = 1.199   | m = 3.62   |

|                                       | n = 0.1216 | n = 0.583   | n = 0.174  |

| $I_{\rm D}(V_{\rm D} = 2.5{\rm V})$   | k = 1.372  | k = 1.261   | k = 40,052 |

|                                       | m = -1.818 | m = 1.115   | m = 4.7    |

|                                       | n = 0.156  | n = 0.370   | n = 0.181  |

| $I_{\rm D}(V_{\rm G} = 1.5  {\rm V})$ | k = 3.264  | k = 3.005   | k = 16,400 |

|                                       | m = -1.982 | m = 1.982   | m = 2.95   |

|                                       | n = 0.156  | n = 0.8833  | n = 0.26   |

| $I_{\rm D}(V_{\rm G}=2{\rm V})$       | k = 1.662  | k = 1.531   | k = 13,160 |

|                                       | m = -1.677 | m = 1.719   | m = 5.547  |

|                                       | n = 0.156  | n = 0.4498  | n = 0.36   |

| $I_{\rm D}(V_{\rm G} = 2.5 \rm V)$    | k = 1.513  | k = 1.393   | k = 26,340 |

|                                       | m = -1.758 | m = 1.741   | m = 3.44   |

|                                       | n = 0.156  | n = 0.4094  | n = 0.48   |

**Fig. 2.4** Measured L=1.5(+), 2 ( $\diamondsuit$ ), and 3( $\bullet$ )  $\mu$ m, and calculated (—)  $I_D$  % variations with the logarithmic method for different channel lengths ( $V_D=0.5$  V) [21]

Fig. 2.5 Measured L = 1.5(+), 2 ( $\diamondsuit$ ), and  $3(\bullet)$   $\mu m$  and calculated (—)  $I_D$  % variations with the logarithmic method for different channel lengths ( $V_D = 2.5 \text{ V}$ ) [21]

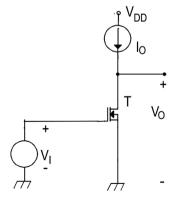

time-dependent functions, a solution was formed for the increasing value of the drain current by the connection of a dependent current source between the drain and source of the PMOS transistor, which was formed for increasing the value of the threshold voltage by the connection of a dependent voltage source to the gate. The proposed model for the PMOS can be seen in Fig. 2.7.

# Concluding Remarks for PMOS Modeling

The effect of hot carriers on the drain current and threshold voltage of PMOS transistors was investigated statistically and an alternative method was proposed to those available in the literature. Three different statistical methods for PMOSs were investigated for modeling the hot-carrier degradation of transistors. In all the investigated methods, the change in hot carriers has been expressed by using two variable functions, and these coefficients can be determined independently of the technology of the transistor and its operating conditions. Considering the correlation coefficients of the investigated methods, we observe that the logarithmic method is the nearest method to 1 with 0.998, and, considering the RMS errors, we see that the

PMOS Degradation 17

Fig. 2.6 Measured L = 1.5(+),  $2 (\lozenge)$ , and  $3(\bullet)$  µm and calculated (—)  $V_{TH}$  % variations with the logarithmic method for different channel lengths ( $V_D = 2.5 \text{ V}$ ) [21]

**Table 2.4** Obtained correlation coefficients for PMOS [21]

|                   | Logarithmic | Power    | Weibull  |

|-------------------|-------------|----------|----------|

| Id (Subthreshold) | 0.998482    | 0.990399 | 0.997737 |

| Id (Inversion)    | 0.997117    | 0.988502 | 0.992571 |

| Vth               | 0.998128    | 0.952594 | 0.9587   |

logarithmic method has the least error with 0.03. From these results, we can say that the logarithmic method is the best method for the explanation of the change in the data. To express the variations in drain current and threshold voltage, models have been proposed for PMOS transistors by using the functions belonging to the investigated methods. By using these proposed methods, the effect of hot-carrier degradation on the CMOS inverter circuit was investigated. Hot-carrier degradation's effect on the performance of the circuit was discussed again by using SPICE simulations with the proposed models. At the end of this work, a lifetime prediction calculation was performed using the proposed functions. The proposed model has some advantages: it can be modeled more practically than the physical model and the simulation time is shorter than the physical model. The proposed method is based on the measurement results and it is independent of the technology; it can easily be

|                   | Logarithmic                           | Power    | Weibull |

|-------------------|---------------------------------------|----------|---------|

| Id (Subthreshold) | 0.03111                               | 0.07891  | 0.04657 |

| Id (Inversion)    | 0.02728                               | 0.04356  | 0.08093 |

| Vth               | 0.01377                               | 0.05528  | 0.08590 |

|                   | · · · · · · · · · · · · · · · · · · · | <u> </u> | ·       |

**Table 2.5** Obtained RMS errors for PMOS [21]

Fig. 2.7 Model to represent time-dependent variation of drain current and threshold voltage caused by the hot-carrier effect [21]

applied to PMOS transistors that have different dimensions. By using this proposed method, percentage changes in drain current, which occur as a result of degradation at any time (*t*) and threshold voltage, can be found and used for the lifetime prediction of the transistor, and/or any other circuit can be approximately predicted.

# Statistical Model of Hot-Carrier Degradation and Lifetime Prediction for NMOS Transistors

# **Modeling of Hot Carriers**

It's known that hot-carrier-induced degradation on MOS transistors causes a reliability problem. In this respect modeling of hot-carrier-induced degradation on one transistor is not sufficient. At the same time, the model has to include the degradation effects on whole circuit, when a known characteristic of the circuit reaches a critical value or how characteristic changes after a critical time. Hot carriers and their effects on the circuits are modeled by two distinct methods. These methods are, respectively,

- Direct parameter method.

- · New model method.

In direct parameter method, hot carriers are modeled by using any existent MOSFET model. In this method, additions or modifications are made on MOSFET model equations for modeling the hot carriers [15, 16]. In new model method, an additional model is added to simulation program. Hot carriers are modeled by using this additional model [17, 18]. Both models have superiorities with respect to other model which are given as below

- (a) Direct parameter method can be only used for selected MOSFET model but new model can be used for all simulation programs.

- (b) Direct parameter method is established on an existing model, because of this fundamental reason improvement of it easy according to constitution of a new model.

### Statistical Methods

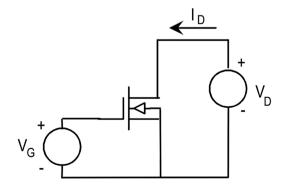

This study was performed for five different transistors produced with the same technology but with different channel lengths. Process parameters of the used transistors are given as  $t_{ox} = 20$  nm,  $x_j = 400$  nm, the dimensions W = 10 µm, L = 1 µm, L = 1.2 µm, L = 1.5 µm, L = 2 µm, L = 3 µm. Stress voltage was applied to the transistors for a duration of 16 h. Statistical methods are applied and investigated by using variation of drain currents and threshold voltages with time which are obtained as a results of applied stress voltage ( $V_D = 0.1$  V,  $V_D = 3$  V,  $V_G = 1$  V,  $V_G = 2$  V, and  $V_G = 3$  V). Calculations are based on linear regression method for the four approaches and least squares methods have been used [17, 18, 21]. So, calculations were performed by using MATLAB program in basis of Table 2.1.

1. Exponential Distribution with Least Squares Method:

$$y = Ae^{Bx} (2.1a)$$

$$a = \frac{\sum_{i=1}^{n} \ln y_i \sum_{i=1}^{n} x_i^2 - \sum_{i=1}^{n} x_i \sum_{i=1}^{n} (x_i \ln y_i)}{n \sum_{i=1}^{n} x_i^2 - \left(\sum_{i=1}^{n} x_i\right)^2}$$

(2.1b)

$$b = \frac{n\sum_{i=1}^{n} x_{i} \ln y_{i} - \sum_{i=1}^{n} x_{i} \sum_{i=1}^{n} \ln y_{i}}{n\sum_{i=1}^{n} x_{i}^{2} - \left(\sum_{i=1}^{n} x_{i}\right)^{2}}$$

(2.1c)

where  $B \equiv b$  and  $A \equiv \exp(a)$ .

### 2. Logarithmic Distribution with Least Square Method:

$$y = a + b \ln(x) \tag{2.2a}$$

$$a = \frac{\sum_{i=1}^{n} y_i - b \sum_{i=1}^{n} \ln x_i}{n}$$

(2.2b)

$$b = \frac{n\sum_{i=1}^{n} (y_i \ln x_i) - \sum_{i=1}^{n} y_i \sum_{i=1}^{n} \ln x_i}{n\sum_{i=1}^{n} (\ln x_i)^2 - \left(\sum_{i=1}^{n} \ln x_i\right)^2}$$

(2.2c)

3. Power Distribution with Least Square Method:

$$y = Ae^{Bx} (2.3a)$$

$$a = \frac{\sum_{i=1}^{n} y_i - b \sum_{i=1}^{n} \ln x_i}{n}$$

(2.3b)

$$b = \frac{n\sum_{i=1}^{n} (\ln y_i \ln x_i) - \sum_{i=1}^{n} \ln x_i \sum_{i=1}^{n} \ln y_i}{n\sum_{i=1}^{n} (\ln x_i)^2 - \left(\sum_{i=1}^{n} \ln x_i\right)^2}$$

(2.3c)

where  $B \equiv b$  and  $A \equiv \exp(a)$ .

### Numerical Results

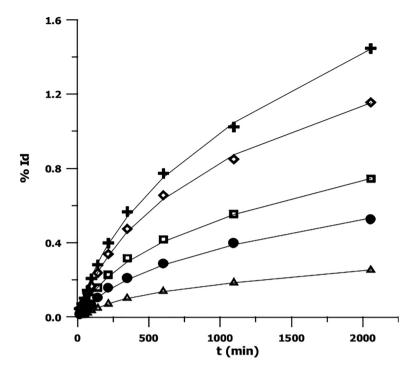

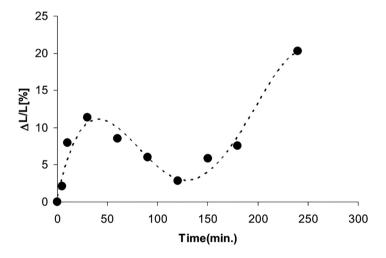

It can be seen from experimental results that the drain current and the threshold voltage of NMOS transistors decreases with time. On the other hand, from a previous study [10], it can be easily observed that the drain current and the threshold voltage of PMOS transistors increases with time. For  $L = 1.5 \mu m$ , the change in the drain current is approximately 4% for PMOS, while it is 0.8% for NMOS. The functions, obtained by using investigated methods, that give the percent changes in drain currents and threshold voltages are given in Table 2.6. The function coefficients obtained of four methods for different channel lengths can be seen in Table 2.7.

Calculated results are compared with experimental results. It has been observed that the Power-log-II method seems to be the best statistical method that characterizes the measurement results. The characterization results, using Power-Log-II method, are given with experimental results (absolute values) in Figs. 2.8 and 2.9. It seems from the figures that there is a good agreement between the experimental

**Table 2.6** Obtained functions of investigated methods [25]

| Investigation method | Obtained function                                       |

|----------------------|---------------------------------------------------------|

| Power                | $\%I_{\mathrm{D}}(t,L) = k \cdot L^{m} \cdot t^{n}$     |

| Power-Log-I          | $\%I_{\mathrm{D}}(t,L) = k \cdot L^{m} \cdot n \ln(t)$  |

| Power-Log-II         | $\%I_{D}(t,L) = k \cdot L^{m} \cdot t^{n} \cdot \ln(t)$ |

| Weibull              | $%I_{D}(t,L) = 1 - \exp(-(t/k \cdot L^{m}))^{n}$        |

Table 2.7 Obtained function coefficients of NMOS transistors for different methods [25]

|                                 | Power                                 | Power-Log-I                           | Power-Log-II                          | Weibull                                         |

|---------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------------|

| $I_{\rm D}(V_{\rm D}=0.1\rm V)$ | k = 1.076 $m = -1.175$ $n = 0.3267$   | k = 0.345<br>m = -1.181<br>n = 1.757  | k = 0.562<br>m = -1.19<br>n = 0.141   | $k = 0.87 \times 10^6$<br>m = 3.62<br>n = 0.345 |

| $I_{\rm D}(V_{\rm D}=3\rm V)$   | k = 0.01908 $m = -1.818$ $n = 0.572$  | k = 0.0008<br>m = -1.795<br>n = 3.66  | k = 0.008<br>m = -1.815<br>n = 0.413  | $k = 0.14 \times 10^{3}$<br>m = 4.7<br>n = 0.83 |

| $I_{\rm D}(V_{\rm G}=1{\rm V})$ | k = 0.06235<br>m = -1.982<br>n = 0.36 | k = 0.0112<br>m = -1.841<br>n = 2.158 | k = 0.027<br>m = -1.845<br>n = 0.191  | $k = 0.18 \times 10^4$<br>m = 2.95<br>n = 0.46  |

| $I_{\rm D}(V_{\rm G}=2{\rm V})$ | k = 0.0286<br>m = -1.677<br>n = 0.486 | k = 0.0028<br>m = -1.7<br>n = 2948    | k = 0.014<br>m = -1.719<br>n = 0.311  | $k = 0.12 \times 10^{3}$ $m = 5.547$ $n = 0.66$ |

| $I_{\rm D}(V_{\rm G}=3\rm V)$   | k = 0.0229<br>m = -1.758<br>n = 0.545 | k = 0.0012<br>m = -1.733<br>n = 3.46  | k = 0.0099<br>m = -1.741<br>n = 0.384 | $k = 0.34 \times 10^3$<br>m = 3.44<br>n = 0.8   |

results and calculated values. To show the similarity between the measured and calculated values, correlation coefficients were calculated and very highly correlated coefficients were obtained. Results obtained can be seen in Table 2.8. Moreover, error calculations are achieved with RMS method and the results are given in Table 2.9. It can be easily observed that the error values are very low. With respect to graphics, correlation coefficients and RMS errors, the methods are classified from the best to worst as Power-Log-II, Power-Log-I, Power and Weibull methods, respectively.

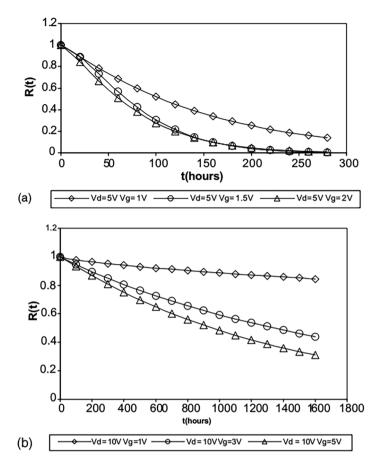

Experimental results at different stress conditions for NMOS transistors are summarized in the three-dimensional plots of  $I_D = I_D(L,t)$  illustrated in Fig. 2.10. As it can be observed from Fig. 2.10 that the drain current decreases with the stress time; furthermore,  $I_D$  also decreases with the channel length.

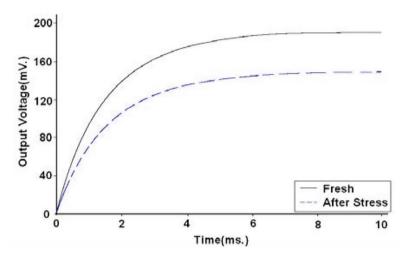

It is apparent from experimental results on test transistors that the drain current and the threshold voltage of NMOS transistors decreases with time. On the other hand, experimental results also show that the drain current and the threshold voltage of PMOS transistors increases with time. The changes in the threshold voltage and in the drain current are represented by connecting a time-dependent voltage source series to the gate and a time-dependent current source parallel to drain-source terminals. According to the observed device behavior, these sources are filled with adequate statistical expressions. The related reliability model for NMOS transistors is illustrated in Fig. 2.11.

Fig. 2.8 Measured L = 1(+), 1.2 ( $\diamondsuit$ ), 1.5 ( $\square$ ), 2( $\bullet$ ), 3( $\Delta$ ) $\mu$ m and calculated (-) %  $I_d$  variations with Power-Log-II method for different channel lengths [25]

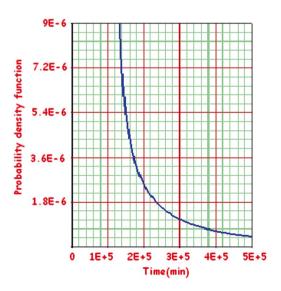

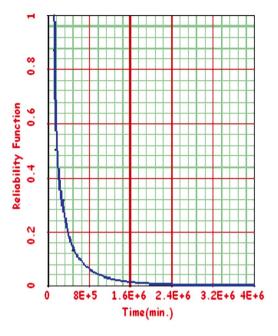

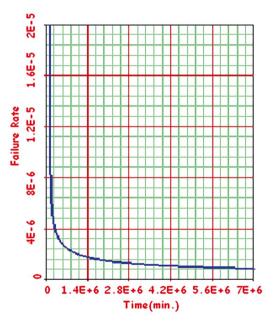

# Lifetime Prediction

Lifetime prediction for NMOS transistors has been performed by using the criteria given in literature [18–25]. It can be reached easily to a 10% lifetime criteria of hot carriers in DC stress application without more time than 10 years. One year in static conditions show 10 years in real operating condition point in analog application. Life time prediction calculations for NMOS were performed with respect to Power-Log-II method by using the functions at the proposed methods and 10% drain current criteria which is given in the literature [18]. Lifetime prediction results obtained by calculations for different channel lengths and different operating regions can be seen in Table 2.10.

# Concluding Remarks for NMOS

In this study, the effect of hot carriers on the drain current and threshold voltage of NMOS transistors were investigated statistically and a method was proposed to be an alternative to those available in the literature. At the end of the investigation, it

Fig. 2.9 Measured L = 1(+), 1.2 ( $\Diamond$ ), 1.5 ( $\square$ ),  $2(\bullet)$ ,  $3(\Delta)\mu m$  and calculated (-) %  $V_{TH}$  variations with Power-Log-II method for different channel lengths [25]

Table 2.8 Obtained correlation coefficient for NMOS [25]

| Channel length (µm) | Power   | Power-Log-I | Power-Log-II | Weibull |

|---------------------|---------|-------------|--------------|---------|

| L=1                 | 0.99614 | 0.99587     | 0.99732      | 0.99615 |

| L = 1.2             | 0.99540 | 0.99613     | 0.99710      | 0.99536 |

| L = 1.5             | 0.99705 | 0.99527     | 0.99744      | 0.99710 |

| L = 2               | 0.99782 | 0.99593     | 0.99818      | 0.99777 |

| L = 3               | 0.99743 | 0.99840     | 0.99927      | 0.99704 |

Table 2.9 Obtained RMS error NMOS [25]

| Channel length (µm) | Power   | Power-Log-I | Power-Log-II | Weibull |

|---------------------|---------|-------------|--------------|---------|

| L=1                 | 0.00702 | 0.00736     | 0.00582      | 0.00731 |

| L = 1.2             | 0.00672 | 0.00622     | 0.00529      | 0.00689 |

| L = 1.5             | 0.00404 | 0.00522     | 0.00377      | 0.00401 |

| L = 2               | 0.00269 | 0.00376     | 0.00248      | 0.00277 |

| L = 3               | 0.00147 | 0.00117     | 0.00077      | 0.00168 |

Fig. 2.10 Experimentally determined dependence of the drain current, on the channel length and on the stress time [25]

Fig. 2.11 The related reliability model for NMOS transistors [25]

was seen that the drain current and the threshold voltage decreased with time for NMOS transistors. Power, Power-Log-I, Power-Log-II, and Weibull statistical methods were investigated by using variation of drain current and threshold voltage with time which is obtained for applied stress voltage. Coefficients are optimized with these methods and functions are generated. These functions give variation of

References 25

|                     | NMOS predicted lifetime (s) |                     |  |

|---------------------|-----------------------------|---------------------|--|

| Channel length (µm) | Subthreshold region         | Inversion region    |  |

| L = 1               | $9.3 \times 10^{2}$         | $3.7 \times 10^{5}$ |  |

| L = 1.2             | $1.8 \times 10^{3}$         | $1.0 \times 10^{6}$ |  |

| L = 1.5             | $9.1 \times 10^{3}$         | $1.8 \times 10^{7}$ |  |

| L = 2               | $5.1 \times 10^4$           | $5.8 \times 10^{7}$ |  |

| L = 3               | $3.1 \times 10^6$           | $6.8 \times 10^9$   |  |

**Table 2.10** NMOS calculated prediction lifetime for different channel length [25]

drain current with time and channel length. The suggested method can be suitable for PMOS and NMOS transistors with different dimensions because it depends on the measured values. Once observed and specified for transistors manufactured with a MOS process the observation results can be applied to the SPICE NMOS and PMOS device models. By using this proposed method, percentage changes in drain current which occur as a result of degradation at any time t, and threshold voltage can be find and used for the lifetime prediction of the transistor.

#### References

- 1. Mitsubishi Electric Co., Failure Mechanism of Semiconductor Devices, pp. 11-15

- 2. A. Bravaix, D. Gougenhim, N. Revil, M. Varrot, P. Mortini, *Effects of High Temprature on Performances and Hot-Carrier Reliability in DC/AC Stressed 0.35μm n-MOSFET's*. Electronic Industries Association Publication. www.iea.org

- 3. R. Thewes, M. Brox, G. Tempel, K. Goser, Channel-length-independent hot carrier degradation in analog p-MOS operation. IEEE Electron Device Lett. **13**(11), 590–592 (1992)

- W. Weber, M. Brox, A.V. Schwerin, R. Thewes, Hot carrier stress effect in p-MOSFETs: physical effects relevant for circuit operation. Microelectron. Eng. 22, 253–260 (1993)

- Y. Pan, A physical-based analytical model for the hot carrier induced saturation current degradation of p-MOSFETs. IEEE Trans. Electron Devices 41(1), 84–89 (1994)

- R. Thewes, W. Weber, Effects of hot carrier degradation in analog CMOS circuits. Micro Elec. Eng. 36, 285–292 (1997)

- 7. W. Weber, Dynamic stress experiments for understanding hot-carrier degradation phenomena. IEEE Trans. Electron Devices **35**(9), 1476–1486 (1988)

- E. Li, S. Prasad, Channel width dependence of NMOSFET hot-carrier degradation. IEEE Trans. Electron Devices 50(6), 1545–1547 (2003)

- Y. Wang, Y. Zhao, B.M. Khan, C.L. Doherty, J.D. Krayer, M.H. White, A novel Sonos nonvolatile flash memory device using substrate hot-hole injection for write and gate tunneling for erase. Solid-State Electron. 48, 2031–2034 (2004)

- F. Kaçar, New Approaches for the Modelling of Hot Carrier Effect in MOSFET's. Ph.D. Thesis, Institute of Sciences, Istanbul University (2005)

- 11. F. Kaçar, A. Kuntman, H. Kuntman, A simple approach for modelling the infulence of hotcarrier effect on threshold voltage of MOS transistors, in *Proc. of the 13th International Conference on Microelectronics (ICM'2001)*, Rabat, Morocco (2000), pp. 43–46

- A. Kuntman, A. Ardalı, H. Kuntman, F. Kaçar, A Weibull distribution-based new approach to represent hot carrier degradation in threshold voltage of MOS transistors. Solid-State Electron. 48(2), 217–223 (2004)

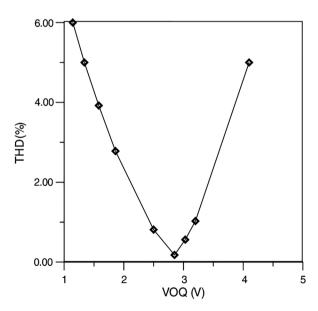

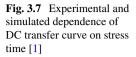

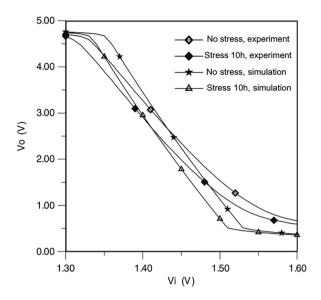

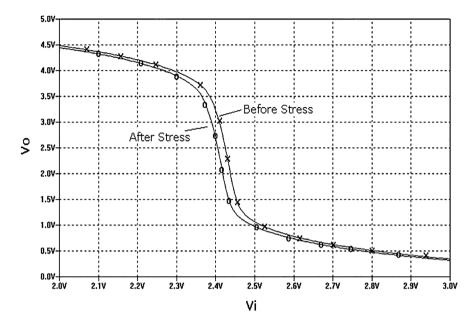

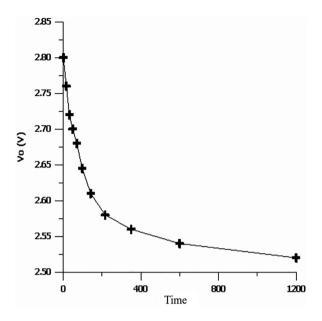

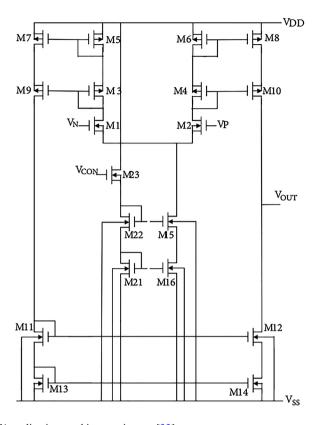

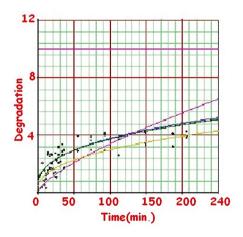

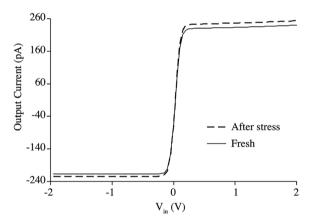

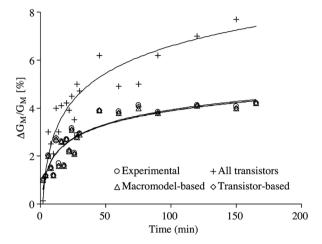

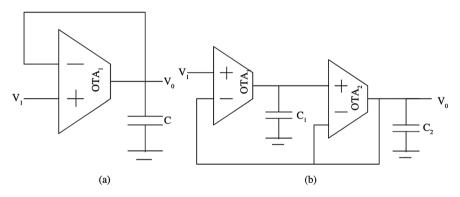

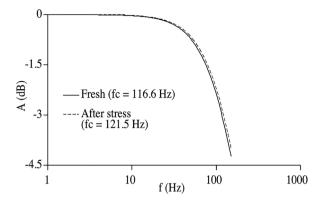

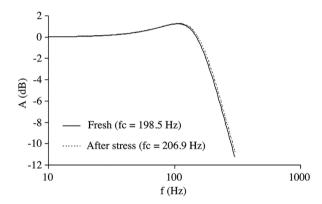

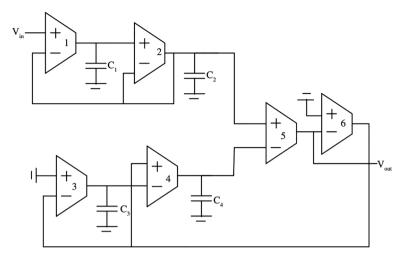

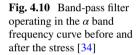

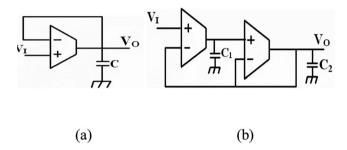

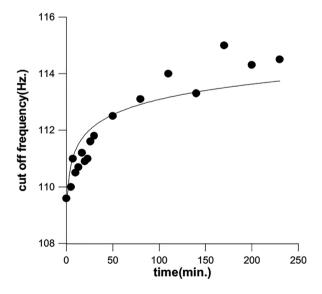

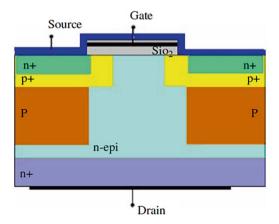

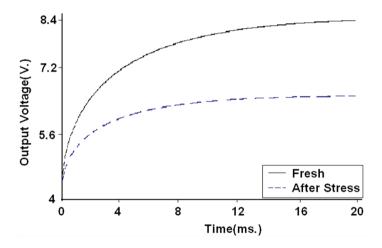

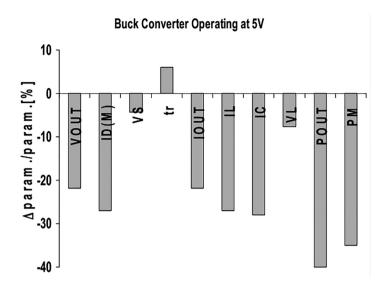

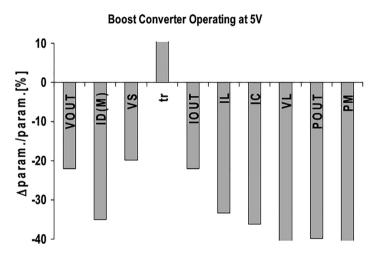

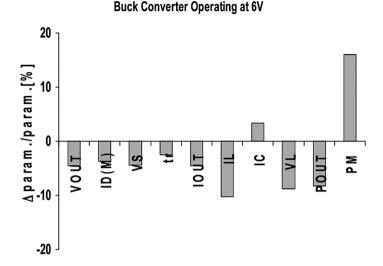

- 13. G. Düzenli, Development of MOSFET Models Suitable for Simulation of Analog CMOS Circuits After Hot-Carrier Stress. Ph.D. Thesis, supported by ITU-ETA Foundation, Siemens Türk A.Ş. İstanbul Turkey and Siemens AG München/Germany under research number MW-/ Kuntman\_J303.0), Istanbul Technical University, Institute of Science and Technology (2003)