Daniel J. D. Sullivan, Eric J. Carleton

# FAILURE ANALYSIS

HIGH TECHNOLOGY DEVICES

Daniel J. D. Sullivan, Eric J. Carleton Failure Analysis

#### **Also of Interest**

Atomic Emission Spectrometry.

AES – Spark, Arc, Laser Excitation

Heinz-Gerd Joosten, Alfred Golloch, Jörg Flock and

Susan Killewald, 2021

ISBN 978-3-11-052768-1, e-ISBN 978-3-11-052969-2

Chemical Analysis in Cultural Heritage Luigia Sabbatini and Inez Dorothé van der Werf (Eds.), 2020 ISBN 978-3-11-045641-7, e-ISBN 978-3-11-045753-7

Electrophoresis.

Theory and Practice

Budin Michov, 2020

ISBN 978-3-11-033071-7, e-ISBN 978-3-11-033075-5

Rubber Analysis.

Characterisation, Failure Diagnosis and Reverse Engineering

Martin J. Forrest, 2019

ISBN 978-3-11-064027-4, e-ISBN 978-3-11-064028-1

Daniel J. D. Sullivan, Eric J. Carleton

# **Failure Analysis**

**High Technology Devices**

#### Authors

Dr. Daniel J. D. Sullivan EAG Laboratories 1708 McCarthy Boulevard Milpitas 95035 United States of America djdsullivan@gmail.com

Dr. Eric J. Carleton

EAG Laboratories

810 Kifer Road

Sunnyvale, CA 94086

United States of America

eric.carleton@gmail.com

ISBN 978-1-5015-2478-3 e-ISBN (PDF) 978-1-5015-2479-0 e-ISBN (EPUB) 978-1-5015-1647-4

Library of Congress Control Number: 2022941691

#### Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available on the internet at http://dnb.dnb.de.

© 2022 Walter de Gruyter Inc., Boston/Berlin Cover image: matejmo/iStock/Getty Images Plus Typesetting: Integra Software Services Pvt. Ltd. Printing and binding: CPI books GmbH, Leck

www.degruyter.com

This book is for all those that toil in the labs, the fabs, and the field figuring out what went wrong so that technology may progress.

Dan Sullivan – Dedicated to my wife Christie and the doctors and staff at UCSF without whom I would not be here to write this book.

Eric Carleton – Dedicated to my parents, Boots and Barbara Shumway, and the medical staff at NBBH, Billings Clinic, and the Mayo Clinic without whom I would not be in a position to write this book.

It is the intentions of the authors to donate any royalties they receive for the sale of this book. The donated proceeds will go to the Multiple Myeloma Foundation (https://www.myeloma.org/) and the Epilepsy Foundation (https://www.epilepsy.com/) to help increase outside awareness, to fund research, and pursue cures.

We are keeping the movie rights money. We have always thought that a sitcom called "Life in the Lab" based on craziness of high-tech labs could be good and accidently educational.

### **Contents**

Index — 121

```

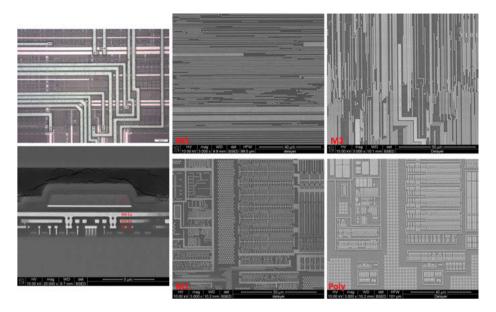

Chapter 14

Cross sections (X-sections) — 73

Chapter 15

Parallel lapping (p-lap) --- 83

Chapter 16

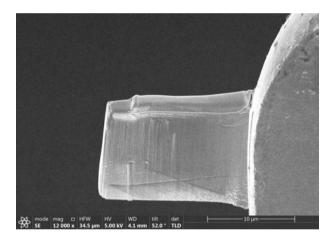

Focused Ion Beam (FIB) — 89

Chapter 17

Scanning Electron Microscopy (SEM) — 93

Chapter 18

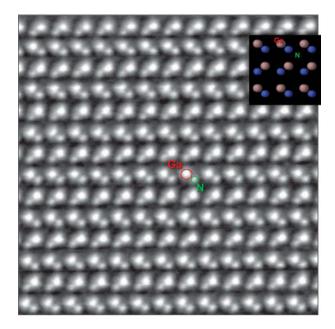

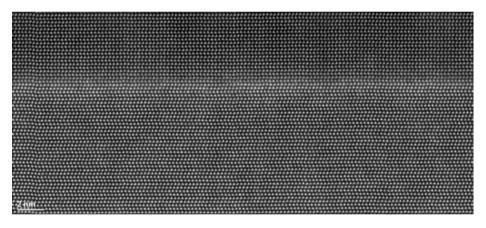

Transmission Electron Microscopy (TEM) — 97

Chapter 19

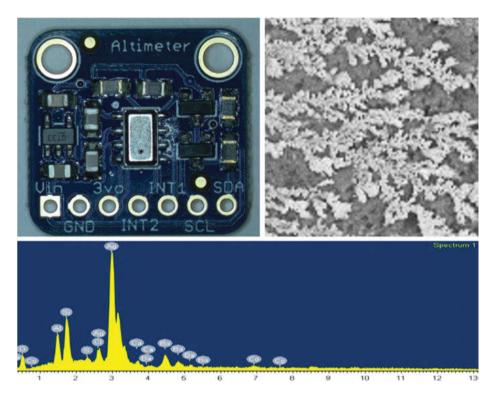

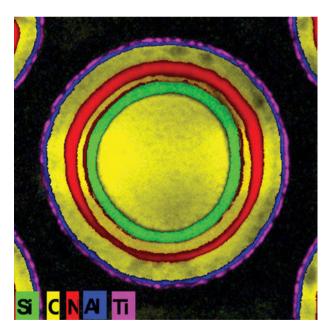

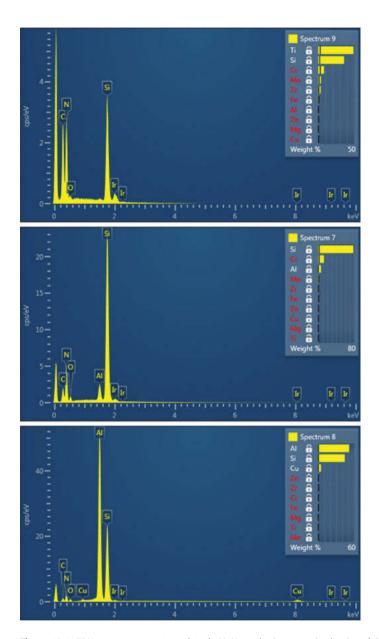

Energy Dispersive X-ray spectroscopy (EDX) —— 101

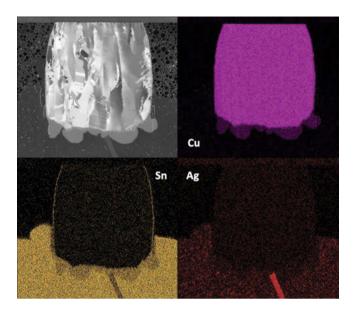

Chapter 20

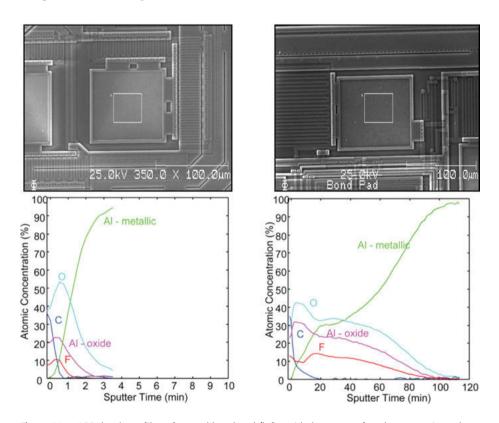

Use of additional materials analytical techniques and processes — 105

Chapter 21

How should these results be used? — 111

References — 113

Appendix — 115

List of figures — 117

```

## Chapter 1 Introduction to FA

The world of failure analysis is large. We hope this work will encourage new comers, give a broader range of knowledge to the journey men/women, and give some familiar and funny examples to the old timers. In this book, we will attempt to cover only the corner of the FA world considering high tech devices and materials. So, we will leave out buildings, bridges, dams, and other large objects, as well as the mysterious area of software. The failure investigation investigating why a system fails (a phone, television, smart watch, or any other device made up of several components) is different than the FA of a single part (resistor, chip, tube), although these are in turn made up of smaller parts themselves. No matter the subject of an investigation, the goal of FA remains unchanged. To find out what caused the failure: the root cause. Even finding the root cause is rarely the end purpose. Knowing the cause allows the factory to change the processes used to make the part, to repair or clean the tools that contaminated the process, or the engineers can perform a design change to improve the end product and greatly reduce or eliminate the failure. Occasionally, the root cause determination is for the purpose of assigning responsibility in litigation/ criminal actions or other situations when the improvement of the device is not the driving purpose. This is why failing parts are sometimes referred as "golden units", in that they are rare and valuable. They offer a chance to better understand and improve a device or process or decide who gets the gold in litigation matters. These parts are also sometimes referred to as "incident units"; however, this nomenclature is often discouraged by attorneys as it sounds bad.

**Figure 1.1:** Image of an ant and a VCSEL (vertical cavity surface emitting laser). The path to the discovery of a failure can sometimes lead you to very unexpected events, like the classic "bug" in the system. Image by Jason Tan.

Failure analysis often accompanies reliability testing of products. The reliability tests are done to determine if a part will last as long as it is intended or determine the failure rates of parts when they are in the field. The warranty people are very interested in these answers. In some instances, the reliability or stress tests are done until the parts fail, this allows inspection of the types of failures that occur thus identifying the weaknesses of the material or design.

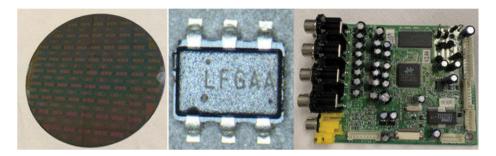

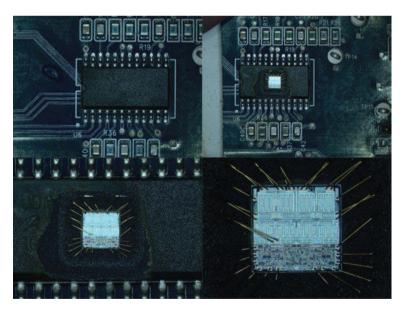

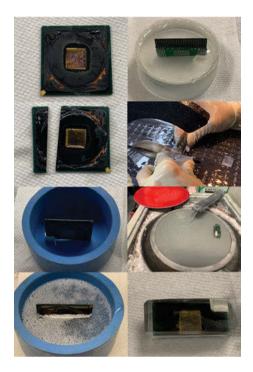

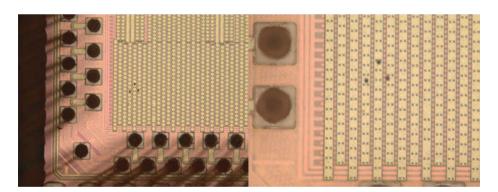

In this book, the parts are typically three types: wafers, devices, and PCB systems. Of course, some of the processes here can be used on any physical object from steel tubes to tennis shoes.

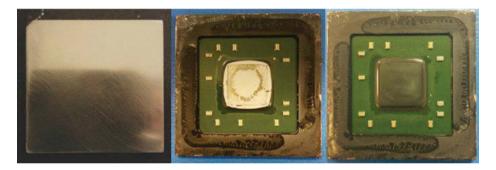

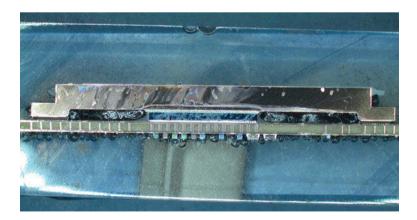

Figure 1.2: Image of wafer, packaged device, and PCB system. Image by Dan Sullivan.

It is also common that customers require a qualification of new parts or whenever a change is made to a device that alters its fit, form, or function. This often requires a written notification to the customer along with a requalification of the device. I have heard many arguments over what constitutes a real change and if a part can be requalified by extension in that it is substantially like another part that has already been tested and passed. Most of these arguments are near-sighted attempts to speed up the shipping of parts to hit a monthly goal and regularly come back to haunt the company later. In larger companies, factory processes such as "Copy Exactly!" are utilized to control and mitigate these issues.

In a Material Review Board (MRB), I have heard a director of packaging say that only the size, the materials for underfill, and the layout were changed, so the device was essentially the same. This was an attempt to avoid having to requalify the device. In this case, I am proud to say he was overruled.

In these qualification tests, there are usually several standard tests that just change the temperature, humidity and the bias the parts experience. Elevated temperature (HTOL) and humidity (DH) as well as swings in temperature (TC) are commonly used to test and qualify ICs. The duration and severity of the tests depends on the industry involved and the desired rating of the device as well as the customer demands. These tests can take months to complete and involve hundreds of

parts, so this is not cheap. When a part fails in a qualification, the FA must be very thorough and fast. There can be millions of dollars at stake so no pressure.

The specific test in which the failure occurs in must be known to the FA team. The main question will be: "Is this a legitimate failure or not?" Knowing the test the part experienced will help direct the FA and rule out some failure modes as not possible. If it is a legitimate failure then the qualification may fail requiring a repeat of the qualification test that failed or even redesign of the product. These repeat tests cost a lot of money and even worse will delay the product time to market or possibly result in the cancelation of the project.

If the failure is not legitimate then that sample may be put aside and one of the extra parts (there are always a couple of extra parts run) is used instead. There will be a lot of pressure brought to bear to have this false failure as the conclusion of all FAs in a qualification. You must be able to resist such pressure and be impartial as an FA person. If you ever compromise your judgment and provide false results or conclusions you are done. No one can believe you going forward. Even if you save the project or company for a while by providing false evidence you will be damaged and unlikely to have any sort of future in FA. Remember you are not the cause of the failure, you are there to provide the best analysis and truthful results so others can make informed business and safety decisions. In cases that involve litigation, or the potential thereof, properly reporting so-called negative results can assist in avoiding additional harm and damages as well as save you from exposing yourself personally in any legal matters.

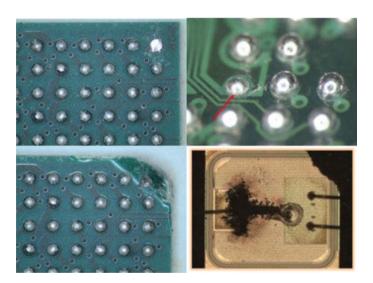

Figure 1.3: Examples of false failures found during qualification testing. Sheared solder ball, insufficient solder, package damage, and ESD damage. Image by Dan Sullivan.

The other major source for FA parts is field returns. They are much less desirable as this means a customer has experienced a failure of your device. While less desirable, they are also very valuable to the FA lab and the company as a whole as they offer an insight into failures under real operation conditions and even though the customer may be unhappy that they have a failure, the FA process offers a chance to show them that you take the issue seriously, that you are professional and competent as a company. Hopefully, once the FA is complete, you will share the information with the customer and it will lead to improvements in design, manufacture, or operations instructions. This should improve the product and the relationship with the customer.

Remember that no one wants to pay for FA or reliability testing and many companies try to get out of it or do the least they can. They are idiots. When done properly, FA and reliability help improve yields, reduce warranty returns, and provide a good company/product reputation. Everyone understands that things can go wrong. Addressing issues with interest and openness will help the situation when they occur.

FA is a tool for companies to use to improve their products, cut costs, and ensure customer satisfaction and safety. When properly staffed and funded, FA is a benefit to the company for controlling costs and enhancing reputation. Failure analysis, and for that matter all testing, can be done in house or through external vendors. The place the FA is done does not matter as long as it is done properly and with integrity. Any company that wants to make decisions based on false evidence or blindly by ignoring available opportunities to understand the issues is not long for this world.

I have been asked many times if it is better to have FA in house or just use outside labs. I have run both types of labs and the answer is of course – it depends. If you have a cutting edge or defense-related technology then security is a large concern and in-house labs have some advantages here as the devices never have to leave the custody of the company. Before entrusting samples to an outside vendor an audit or at least a visit to the site is advisable. Do they have a secure location for sample storage when not being worked on? Do they have a secure server system for the results and reports? What is their policy on sharing results? What is the process for screening the individuals that have access to your parts? All these questions should be answered to your satisfaction before you move on to the next questions. Additionally, a non-disclosure agreement (NDA) is almost always a requirement before any work or sharing of IP details is begun.

One additional detail on military devices is ITAR (International Traffic in Arms Regulations). There are rules as to who may work on or even be in the room when such devices are present. If you will be working on ITAR parts for FA, you and your company need to understand the rules and processes that must be followed. I do not want any of the readers of this book to end up in federal prison. There are many specifications for testing and analysis, but this is the only one I know of that can carry felony charges. You will have to learn what a "US person" means.

Turnaround times (TAT) and cost are the next big issues. I have yet to meet the person who does not need their results very quickly – yesterday or the day before is fine. If you have ways to triage work coming into the lab that is best. If every curious Karen's work must be done and there is no ranking of importance you wind up with FIFO, first in first out, which is a terrible system, only slightly better than the squeaky wheel system. The best triage systems are based on cost: no one pays for unimportant work. For internal labs where cost is not possible to use, a limited number of slots allowed in the lab for each "customer" division works well. It is even better if they have rankings for their slots. So, if VP Joe wants an FA done immediately, they use their #1 slot and if that is currently occupied, they replace the other request with this more important one. At one lab I ran, we provided laminated cards with 1, 2, 3, and so on printed in large font on both sides which were handed to the VP of each department that provided funding to the lab. Each had the name of the department and a color making it easy to identify. The total number of cards was based on each person in the lab working on five jobs at any given time. This number was based on how many fingers I have on one hand and is somewhat arbitrary, but something between 3 and 10 projects is the most a person can juggle reasonably. The number of cards/projects each division received was based on the percentage of the FA budget that division provided. This worked remarkably well. Unfortunately, I have also run labs in companies that believed every job submitted needs to be done and nothing has priority. If you guessed, I had constant calls about the newest hot job that had to go first, you are psychic. With no allowed method of triage, it became a game of which VP called me last. This was a waste of my time and theirs.

Using something like the ranking cards, the departments are able to decide which of their work requests should go first and what is not important enough to get a slot. This also makes very clear to all parties the resources available. The lab resources for each department is directly related to the support the lab receives. This made discussion of the budget for the FA lab much clearer for all involved. If they added support for an additional headcount, then five more cards would become available and the departments that put in the support would get the cards, easy.

The costs are always an issue. The cost of doing work internally is of course the cost to set up the lab: space, people equipment, upkeep, and usually some work with the fire department and health department. This is a large obstacle when first setting up a lab as opposed to smaller expansions to an existing lab. When deciding to set up a lab or not or adding substantial staffing or capital equipment an ROI (return on investment) sheet should be done.

The ROI is fairly easy to do. Determine the full costs of what you are adding, say a new X-ray imaging machine that will take up a 10 ft by 10 ft area in the lab and require a technician to run. Get the tool costs from the tool vendor, say \$100,000 in this case. Say the monthly cost of the lab space all in, get the actual number from

your facility manager, is \$2 per square foot. Now the technician you are hiring you can estimate from current staff salaries or HR can help you out here, let's say it is \$50,000 per year. If the upkeep is minimal, no major process gases or other materials, then along with power is only \$200 per month. So, amortizing the tool cost over 5 years, good luck with that as it is quite often 3 years or even 18 months in some companies, a total yearly cost is \$20,000 for the tool plus \$2,400 for the space plus \$50,000 (assuming HR does not add in the extra costs for employees like insurance and so on) plus \$2,400 for supplies and overhead. This gives us \$74,800 yearly cost in years one through five, ignoring inflation. So, if you are not spending at least this much, or have very definite plans to do so, the purchase does not make economic sense.

If you are spending substantially less than the calculated yearly costs, then this is when using an outside vendor for X-ray imaging should be strongly considered. If you do have plans to spend this amount or slightly more, then a thoughtful discussion and business decision should be made. The pros and cons listed out and comparisons to outside vendors should be considered. Apart from the costs the factors of security, dealing with staff, available lab space, and needed certification by state and local authorities for some lab functions, as well as the time and effort spent by the company on work not in the core capability of the company should be considered.

If you are spending 2x the yearly cost of the set up you should very strongly consider doing this work in house. If the decision is made not to go with the internal lab you should then have a conversation with your outside lab(s) about the awesome deal they are going to make for you not to set up your own lab and continue using their services. Long term, a year or more, agreements with discounts or set costs should be used to secure what you need in terms of costs, turnaround times, and volume of samples.

It is important to have people in your company that can understand and interpret FA results whether the work is done internally or with outside vendors. Otherwise getting results from labs will be a wasted effort if no one in your company can understand what is possible in an FA or has any idea what the results mean then you will likely be paying too much for too little.

# Chapter 2 Why is FA important?

Many people do not understand the benefit of reliability testing and failure analysis work. These people are short sighted. Every time there is a failed device, it is an opportunity to better understand the weak spots in design, materials, and production of the device and this can lead to improvements.

Anyone who complains that reliability and FA are just unneeded costs should think about the announcements on planes a few years ago that a particular brand of phone was not allowed on board due to fire hazards. The costs of recalls, lawsuits, and the missed opportunities to improve yields far outweigh the costs of FA and reliability. A line down situation can run into costs of millions of dollars a day.

Figure 2.1: Cell phone on fire. Image by Dan Sullivan.

I was on a plane several years ago when the announcement over the plane's speakers said, "If you have a XXX cell phone you will have to leave it at the gate or deplane." No one wants that publicity for their company and product. This was a direct result of management at XXX ignoring and/or skipping reliability and FA testing and results. When the product fails a qualification and the FA results show a problem, bad management will blame FA and try to get you to change or gloss over the issue to get the qualification to pass. When the disaster hits and massive returns occur, they will be just as quick to throw FA under the bus and state that, "It is your responsibility to report such issues."

You must never bow to pressure to give false or half-true results. It is far better for you to be fired because you would not fudge or shade the results than to knowingly state false results. Being fired for sticking to principles is a badge of honor to wear and will lead to other better opportunities as well as shield you from litigation

implications. It will also damage those who pressured you and that company will either have to replace them or fail. When I was told to stop doing reliability testing because some results were not favorable, I immediately started looking for another job. That company is of course dead now.

Bad things happen when FA and testing results in general are ignored. When the space shuttle Challenger blew up in flight, it killed all on board. I believe this tragedy is directly traceable to bad management ignoring materials and reliability engineers. Along with other issues, the O-rings used on the shuttle were made from a material, buna, that loses its sealing properties when cold. The tests showed this issue and other concerns for the heat shielding and the very poor management overrode these concerns and went ahead with the launch. This ignoring of data and results of testing led directly to this failure. If the O-rings had tests that resulted in failure and FA was done that showed what should have been the obvious, that the material used for the O-rings is not good in cold conditions and a different material or sealing system was used, then this tragedy may have been avoided.

Good companies do FA and successful companies learn from the analyses and improve. So, in the end, the failure analysis is a guiding light that enables us to make better/safer things.

Internal and external FA support is very important. If you are developing a new product or improving an older design, and you cannot inspect the results, you are not going to make much progress by trial and error without a feedback loop. If, really when, a defect makes the product fail for whatever reason, it is important to see and understand that defect and its cause(s) so the design or process can be improved. The reasons to want to do this are many, but the main ones are: the customer will not buy the product if it has an issue that is not explained, the customer will not continue buying a product if the field returns are going up and no reasonable corrective actions are put in place with evidence that they will address the issue, you do not want to make a crappy product out of pride, you do not want to injure or kill people out of a moral sense and/or fear of litigation and possible criminal problems, the warranty returns are going to end your business. All of these are legitimate reasons to want FA done right and quickly.

There are some industries where these issues are more relevant than others. If you make flip flops for people to wear around the pool you are unlikely to kill anyone, but you do not want chemicals from the flip flops to turn people's feet green. If you make a cat's toy and it breaks in a month no one cares, but it better last a month or the returns will get ugly. If you make IC chips that control a plane's navigation system you do not want any failures at all, as many lives and lots of money are in play and any incidents will be very high profile. Risk versus severity for failures will determine if you need to do an FA on each failure and what you are willing to spend on these efforts.

Ideally, through the testing and FA work, all the issues will be found, analyzed, and worked out before a product goes to market, or to any customers. This is rarely the case as time to market pressures are enormous and companies all strive to get to market first as market share is largely determined by who is there first. Business decisions can be very difficult and having accurate information available quickly is a great help.

FMEA (Failure Mode and Effects Analysis) is a process used to call out possible failure modes, their likelihood, and their effects. This enables testing to be prioritized to cover the most common or most severe issues. As issues are resolved, the FMEA is updated and testing priorities adjusted. While not directly FA, it often involves FA and drives testing. When used properly, it can save companies time and speed the product improvement cycle. When used only because it sounds fancy and no follow up occurs, it is a total waste of time.

## Chapter 3 Planning out an FA

In approaching failure analysis work, it is always best to have a plan before touching a part. Initial optical imaging of the incoming part is also very important. Many steps in an FA cannot be undone and so an initial plan including review steps when results are obtained greatly increases the chances of success. Now, it must be said that FA is not a 100% success business. Often the process involves spraying hot acid on parts, grinding, and polishing to hit an exact or sometimes unknown location. Even the electrical checks can sometimes cause issues in the sample under study. One of the first questions should be: "Are there multiple samples or only one?" This answer will greatly affect the FA options.

When doing the initial steps on an FA with an electrically live part, there are precautions that should be taken. Many of these steps should also be observed on electrically dead or nonelectrical parts as well to avoid the inducement of false damage.

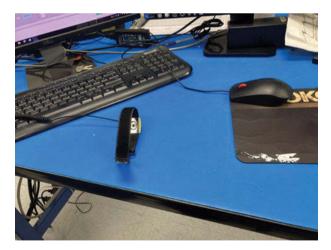

First ensure that ESD (electrostatic discharge) mitigation is in place, humidity is in acceptable range – usually 30–90% RH (relative humidity), floors are treated with dissipative wax or are ESD floors, and the people handling the samples are trained in ESD rules, wear smocks, shoes, and wrist and/or heel straps that are ESD compliant and tested every day. The samples are worked on table tops with ESD mats, the chairs are ESD type and linked to the floor (usually by a short chain), the parts are transported in ESD appropriate bags/boxes, and so on. A typical ESD workstation is shown in Figure 3.1.

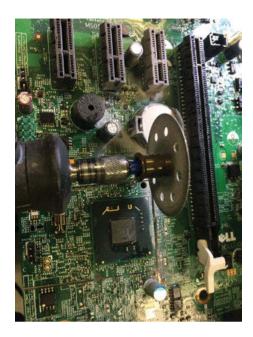

**Figure 3.1:** ESD work station for a C-SAM tool. Note the blue electrostatic dissipative mat and wrist strap near the keyboard. Image by Dan Sullivan.

There is no worse FA result than a false defect. It masks a real defect and has operations chasing their tails trying to solve an issue that does not exist.

I have received many samples that are not in proper containers and then customers wonder why the parts show a new failure signature at the lab. I have even had customers pull parts out of their pockets and hand them to me, complete with lint all over the surface. At least they do not shuffle their feet on carpet in the lobby and then touch the spot with their fingers to show where the issue is located. Oh wait, I have seen that too. Part of FA's job is to educate their customers.

If your company makes steel bolts, you will not be caring much about ESD but if you work with ICs and your company does not want to take the proper ESD precautions due to cost or difficulty, then you should be looking for a new job. You should also insist that the lab doing FA work for you has a robust ESD process including a SOP for handling ESD-sensitive samples. An example of typical ESD/EOS damage is shown in Figure 1.2.

If possible, you should have a written specification on how samples should be turned in to the lab. Share this with your customers as it is in both your and their best interest to find the actual cause of failures and not how carrying a part in a pocket causes damage to a sample. This is important for both general samples and ESD sensitive ones, and an additional reason to thoroughly optically image and document incoming parts. ESD bags/boxes are your friends. The lab may have to invest in a supply of these and provide them to the customers.

The first standard operating procedure (SOP) for a lab should be to have a specification and form for submitting FA requests. In this it is important to know when to be hard and when to let items slide. For a 5-min inspection with an optical scope or a check in the X-ray to see if the sample is correct or if anything can be seen at all, I suggest skipping the formal submission process. This will win you friends and keep paperwork that is longer to fill out than the actual analysis to a minimum. For these cursory, pro-bono inspections, it is a quick look only with no saved images. For anything that takes more than 15 min, or they require the images, always insist on the paperwork and the assignment of a job number in your system. In some situations, and with some customers, you might need to tie the release of the images and data, with the completion and submission of the form. If they do not have time to complete the submission form fully, then the work must not be very important and it should be put aside so the lab can work on more important issues. Do not let weasels run your lab.

Next week, when they need the images or a report for what was seen in a meeting and you are asked for the report, you will be glad you have a job number and everything saved in the right spot. They may try to get out of the formal submission process by saying it is just a little thing and the data stays with them. They lie and it will be your fault that there are no saved images later when your boss or theirs wants to see them. So, do not tolerate a loose work ethic for the data on jobs or submission processes. This will also be a great help when you are asked to justify current staffing or hires and new equipment purchases. If all the jobs are in the system, it is easy to later calculate the costs of the work if done at an outside service lab.

The idea of official FA process controls and documentation is often not well received by the lab staff. I used to think this way as well when I was young. I have learned the hard way why these documents are valuable and even helpful when used correctly. There should be an official document for submitting a job, which either has a form (traveler that will then accompany the samples) or a list of the information required for a request to be accepted. Without this, you are in the Wild West and you are not the cowboys. I have received samples with no instructions or just a part number. If you do not know who the requestor is and how to contact them then you are stuck. Just put such requests aside and forget them. They are obviously not very important to the customers as they have done such a terrible job submitting the work. If you have official documents describing the correct way to submit jobs, you are fairly bullet proof from this type of customer who just wants to dump the work and then blame FA.

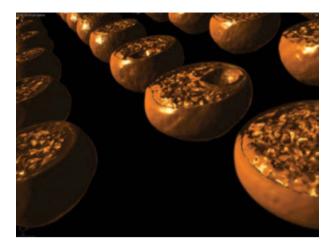

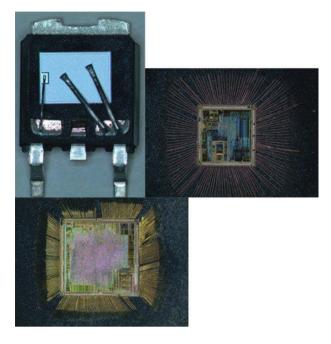

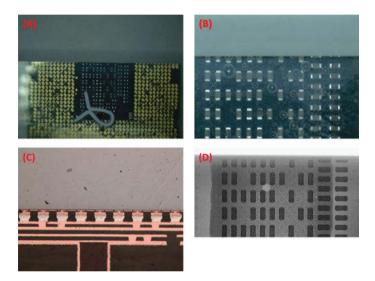

It is important that you become an expert on the samples you and the lab are working on. It is not so important that you know everything right away, but you need to learn what the samples do and how they should behave. It is also very important that you learn the proper terminology. If you call the devices the proper name and all the components as well, it will not be noticed. However, if in a meeting or a report you call the solder bumps solder balls and the plugs M1 it will be apparent to others that you don't know the difference. The difference between solder balls and bumps is shown in Figure 3.2. This will adversely affect your standing with others and the trust they have in your results will suffer. It is better early on to admit a lack of knowledge and get the correct answers than three months into a project be caught using the wrong terms. This is even more important when dealing with paying customers. So have a pre-analysis meeting to get all the information you need from the customer including the proper names and terms. We saw some gunk on the thingy mebob is not going to go over well with the VP or the customer.

I have had to attend weekly meetings at one company just for damage control. Some engineers would hold onto work all week and then dump all the requests into the FA lab on Friday afternoon. In Monday morning meetings, they would then say, "I don't know, the requests are held up in the FA lab."

After a very interesting call with my boss and the VP of the packaging group it was decided I should attend the next meeting of the packaging group. Some of the engineers were not thrilled to see me at the Monday morning meeting.

Once I started attending these meetings and called out the day and time each request was submitted, this behavior stopped. Unfortunately, it required me to attend meetings in a different building from the lab in person to put an end to what should have been an obviously wrong approach. It is always better to sacrifice some time up front to correct a process gone wrong than to wait and hope it fixes

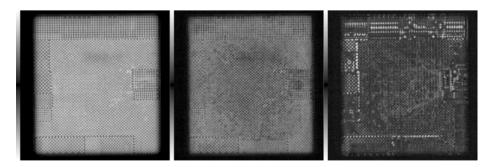

Figure 3.2: 3D X-ray image of FC device with solder bumps (little ones) and solder balls. Image by EAG.

itself. This may mean an unpleasant discussion or confrontation, but better early than once it reaches unbearable levels.

Next, you need written procedures for each of the major activities the lab performs: Receiving work, optical inspection, decap, SEM, and so on. These procedures should not go into painful detail. For example, in a cross-section SOP, you do not need to call out each type of polishing sheet to use and for how long, just write "use polishing sheets as appropriate and until scratches are removed or all scratches face in the same direction for each polishing sheet used." The training should then fill in the gaps. These are also very useful as cheat sheets for techniques the staff do not use every day. A section on how to turn on the tool, collect and save a spectrum and/or image and a section on how to properly leave the instrument is very helpful. Also, to be prepared for unfortunate events when the power goes off suddenly or the machine needs to immediately be shut down, a section on how to properly power off tools and how to restart them is great. The contact information for service and vendors for the consumables or frequently replaced parts should be included in this document and all the lab staff should be trained on this process.

I almost hate to have to say it, but these documents are worthless if you do not use them. Train people with them. The first step to learning to use a tool should be to read the SOP (standard operating procedure) document for the tool. The SOPs must be either hardcopy in the lab or *easily* accessible online. Talk with your QA people to get this right and insist they do it the way you want – easy to access, or do not bother. I once had QA tell me they were the only ones that could have these documents online and it took only nine layers of nonsense to get to them. Guess how many times these were accessed by lab staff. These geniuses did eventually let

me have hard copies chained to each tool as long as they were laminated and had the rev number and my signature on them. Sometimes, bureaucrats get confused thinking the rules are the reason instead of the actual work.

While I do understand that in a factory you want to ensure that the latest specifications are being used and there needs to be some control over this it needs to actually work. Making it very difficult to use the system just leads to people ignoring the system. Being able to shrug and say "Well they did not follow our procedure" at the end of a disaster is not very helpful. You may need to get support from upper management to make QA do their jobs in a helpful way instead of what is easiest for them.

### **Chapter 4**

### Typical types of failure mechanisms

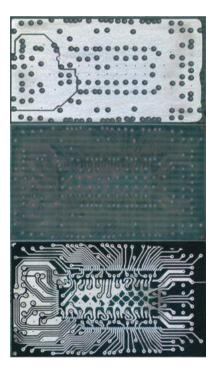

Of course, the typical failure mechanisms will depend on the type of samples you have and their history. Here we will cover those we have commonly seen in the IC and electronics industry. Starting with the wafer or die level failure modes, the most common are: physical handing issues, leakage, high resistance, and opens/shorts.

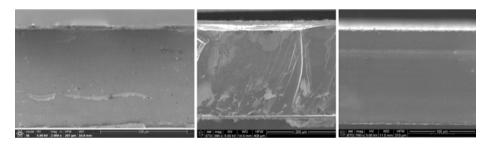

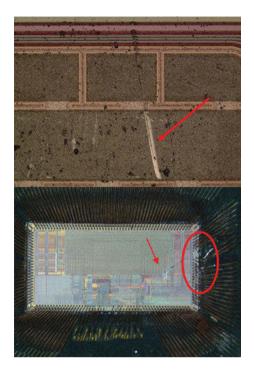

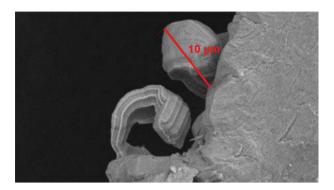

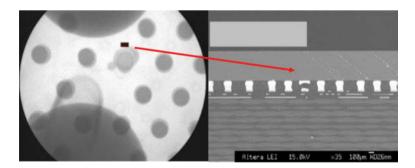

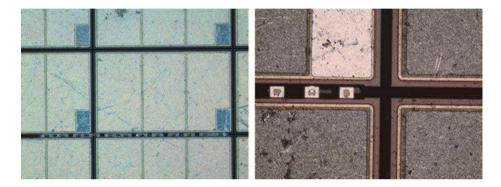

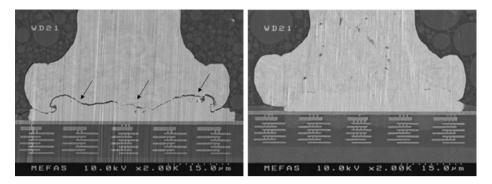

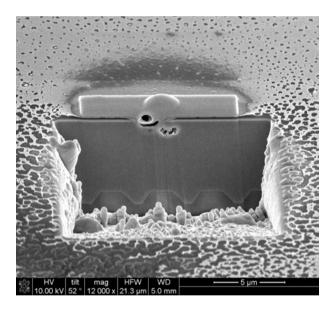

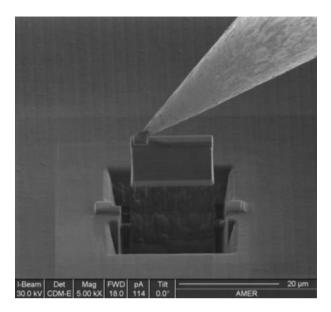

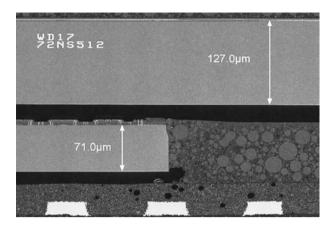

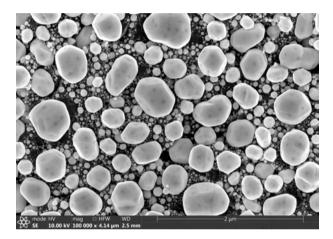

Physical damage is usually caused by dicing, pick-and-place tools, or humans (especially with metal tweezers). There are a variety of dicing methods in use and they vary in their rates of damage and the way they cause damage. Figure 4.1 shows cross sections of several dicing methods. Usually, the dicing damage is caused by a system that is not well maintained or has not been used on this new device. I have seen edge damage from dull blades, loose "chattering" blades, and blades that hit objects in the street (this was a truly dumb idea to place metal critical dimension (CD) markers in the street). Typical scallop damage is shown in Figure 4.2.

Figure 4.1: Die edge damage on two die (horizontal and vertical damage) and a new method of dicing that leaves very little damage. Image by EAG.

Pick and place tools can hit the edge of die if not properly aligned and the rubber suction cups do wear through eventually and cause telltale circular or partial circle damage on the die when the metal tube behind the suction cup is exposed and contacts the surface. This is due to poor maintenance or assembly set up. This type of issue requires inspection in the assembly process after each step to catch and identify the tool(s) responsible.

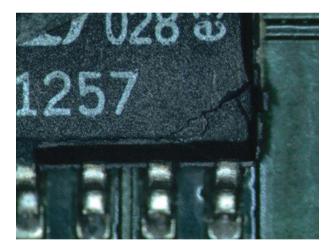

Package damage is more common before a device is attached to a PCB. The corner damage shown in Figure 4.3 regularly results from a dropped part or when devices are improperly seated in a Jedec tray and the lid forced closed.

Humans can cause all kinds of damage, but the most common is the metal tweezer scratches. One issue I witnessed involved assembly of a die which had very good yield on one lot and the next lot had very poor yield. This occurred several times with high yields followed by very poor yields and the FA team observed large

**Figure 4.2:** IR image of scallop damage. The damage is seen through the ~700 microns of Si. Image by EAG.

Figure 4.3: Package damage. Image by EAG.

scratches on the face of the die for the failing units. This cracked the passivation and led to failures in stress testing. When we had observers put on the assembly line, we found the metal tweezers being used to handle the die by one shift were causing the scratches such as those shown in Figure 4.4. Issue solved right? No, the issue came back the week after we removed the observers. We had to have observers go back in for several weeks and retrain the assembly personnel and confiscate some tweezers. Some issues are tougher than others to resolve.

In the case just described, the cause of the passivation cracking issue is obvious. This is not always the case and it is important to consider all possible sources

Figure 4.4: Die face scratches from tweezes, and typical die scratch and wire sweep (inside oval). Image by EAG.

for such damage including inadvertent introduction of scratches and passivation cracking from the FA process and improper electrical testing.

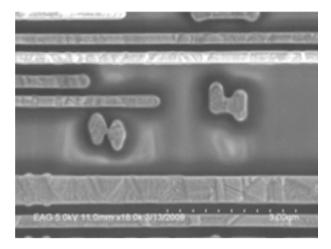

Leakage issue can arise from many root causes. The most common I have seen are: particles and poor etch process. Particles are shed onto the wafer during a variety of deposition and etch steps in the Fab. One of the core results of interest in such an FA is what is the particle made of and the other is what layer is it on. These two items help identify what chamber/process has the issue and needs to be serviced.

The deposition and etch steps of making a wafer involve placing resists down, patterning them, removing the desired material, depositing the metal, oxide, nitride layer and then etching away the extra material and the remaining resist. If the resist does not do what is intended or the etch process is not correct (under or over etch) then too much or too little insulator/conductor may be the result, which leads to leakage paths, opens, or shorts in the device.

The issues that cause leakage are often the same ones that generate opens and shorts and high resistance. In these cases, a larger particle or in a less fortunate position or alternatively the under or over etch is more severe creates a more severe failure.

Figure 4.5: Image of particle in IC at the W plug layer. Image by EAG.

Figure 4.6: High-resistance contact and M5 connection failure. Image by EAG.

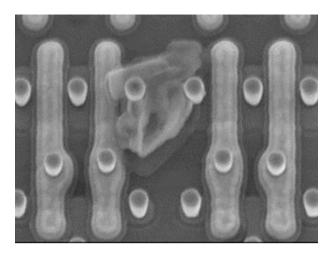

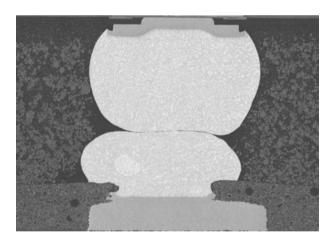

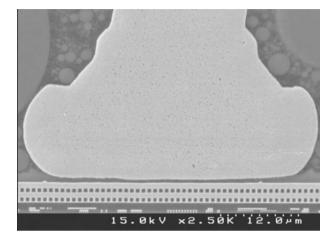

For packaged devices, the above issues in the die may occur on the die inside, but the issues attributable to the package itself most commonly seen involve: solder, delamination, and wire bonding issues.

Figure 4.7: Under-etch pattern leaves too much contact in place. Note: this can also be caused by a patterning issue and the reticle should also be checked. This failure is sometimes called "kissing" as the adjacent metal are supposed to be completely separate but like Romeo and Juliet they find a way. Image by EAG.

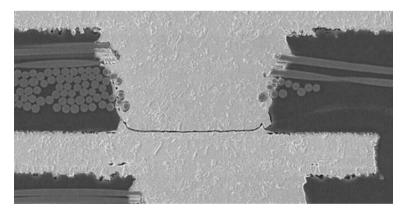

Figure 4.8: Cross section of solder non-wetting, so-called head in pillow (HIP) or snowman bond. Image by EAG.

A common solder issue is non-wetting. This occurs when the solder does not reflow due to an incorrect reflow temperature profile or contamination preventing the solder from making proper contact. Your assembly house should always have the reflow temperature profile for every run. If they do not or will not share it, find a different assembly house. The issue of contamination is harder to get to root cause as the part has been through a reflow which will volatilize many common organic contaminants and getting to the surface of the solder after assembly is not

straight forward. This will require the assembly house cooperation to check for contamination at several points in the assembly process and involve tools like FTIR, XPS, Auger, and EDX.

The typical form of this is called head in pillow (HIP) or snowman non-bond. HIP issues can regularly be found by X-ray imaging (2 and 3D imaging) or by a cross section like the one above in Figure 4.8.

Figure 4.9: FC delamination in the die. This case occurs in a low K dielectric layer. Image by EAG.

Delamination is the separation of layers in the device. These include: the encapsulant to the die surface, layer(s) inside the die (I have only ever seen this with low K dielectric layers), the die-to-die attach, and for flip chip devices the underfill to die or underfill to substrate interfaces. These separations cause electrical opens by pulling the wire bonds up or disconnecting conductive die attach from the backside of the die, and in flip chip, the solder bumps can crack as the underfill no longer supports them. Even layers in the substrate can delaminate. Scanning acoustic microscopy C mode (C-SAM) is the common technique for detecting these issues.

In Figure 4.9, the bright area in the lower right corner is the delamination. This is likely in the low K dielectric layer in the die, but a cross section should be done to verify.

Wire bonds come in many flavors. The standard wire bond materials are: gold, aluminum, and copper. I keep hearing that silver is just about to take off, but I have heard that for five years now and I have yet to see one silver wire bond part except the one we had to be begged to get so we could test decapping it. A typical wire bonding failure is shown in Figure 4.10. The wire bonds can have several attach styles as well. The two main methods involve ball and wedge (also called stitch).

Figure 4.10: Lifted ball bond from inadequate wire bonding. Image by EAG.

These bonds can be double layered and various other combinations including the addition of other materials to help make the bond tougher. I have seen a stitch bond with a ball over it. I have seen silver paint under a stitch bond. These all seem idiotic to me as you now have several interfaces that can fail instead of one and you have applied multiple stresses on the bonding. I have yet to see a study comparing these methods as most of this information is kept as trade secrets by companies and so not made public.

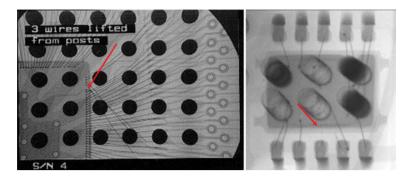

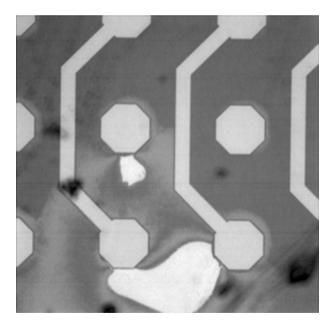

The wire bonding process can create problems. First and most amusing from the FA point of view is when the wire bonding program is incorrect or the device orientation is incorrect during bonding. This is easy to catch as the X-ray image will show the wires not going where they are supposed to in the layout diagrams. There is a pin one location on all devices that I have observed that sets the device orientation. The X-ray image is compared directly to the layout and if the wires do not line up, that is the issue. FA done and report goes out, easy. I have even done a couple of FAs when the bonding wires, once even the die itself, were missing. Now someone in the assembly house has some explaining to do.

The wire bond process involves pressing a wire onto the bonding pad or surface, commonly Al or Au pads, with force, heat, and ultrasonics. This process is worked out by the assembly house, but occasionally they get it wrong. This can be because the materials are new, or the wrong program got loaded or it is not a very good assembly house. The "wrong" can result in either overstress which breaks or craters the die, or understress which results in nonadhesion, and sometimes the

**Figure 4.11:** X-ray image on the left showing several wires lifted from posts on the substrate. The image on the right shows bond wires that have been melted. Image by EAG.

wrong intermetallic phases of the wire and pad are created, like the purple plague. The purple plague is named such as it has a purple color and is very bad as the phase created in the AuAl interface is very brittle and crumbles causing opens. This issue of purple plague was understood and avoided in the 1990s but occasionally creeps back in at some assembly houses.

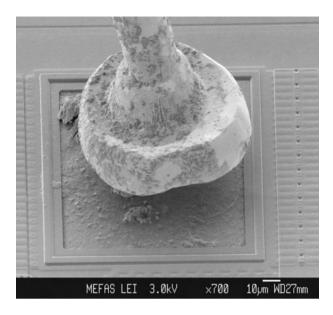

**Figure 4.12:** A cratered bond pad. If the force and/or sonics used are too high, then the bonding will fracture the underlying die and the layers of oxide and traces and even down into the silicon will crack and pull out when the part is decapped. Image by EAG.

The high-end wire bonding tools are amazing to watch as they make many connections at high speed. They make me think of giant high speed sewing machines. When these have alignment issues, it is usually obvious quickly and gets caught by QA inspections in line before the parts get fully assembled. For wire bonding on

smaller scale, this is not the case and issues do wind up in FA. Occasionally, misalignment is so bad the ball bond is not well centered on the pad and this can crack the passivation around the pad leading to leakage issues. The ball bonds ideally are dead center on the pads. The further away from this the more likely issues will arise.

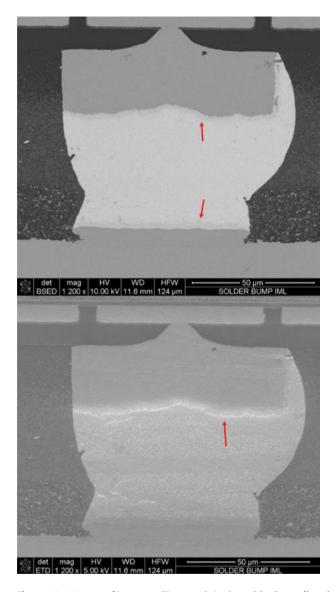

Figure 4.13: Slightly off-centered bonds may not affect the part performance, but once the edge of the pad is hit and the passivation surrounding the pad cracked this will lead to leakage, shorting, and reliability issues. Image by EAG.

The standard wire bond lift FA involves an electrical check at the bench to verify the open/high resistance. Pushing down on the top of the device may cause it to recover, and this is a common sign for ball lift or solder issues. The X-ray analysis will show gross lift but very small, less than 3 microns, is difficult to observe. C-SAM is then done to check for delamination in the wire attach areas which will lift the ball or stitch bonds. The destructive work then begins with a decap. At this point, the wire will lift or very easily be moved by light pressure as the encapsulant is no longer holding it in place. The bottom of the bond and the area under the bond are now inspected by optical microscopy, Auger, and SEM to check for contamination, thick oxide or excessive intermetallic layer (IML) growth. The common results are as follows. No bond was ever made or the pad is cratered both result from incorrect settings on the force of the bonder. The oxide on the pad is very thick and a bond was made but did not adhere. Gross contamination is present and visible. The surface is corroded and the IML is thick and crumbly (check for Cl contamination).

Purple plague is a special case of IML issue. This occurs when the conditions during the bond creation are incorrect and undesired phases of the intermetallic are made. The one called purple plague is very brittle and leads to cracking. It is also a very pretty shade of purple.

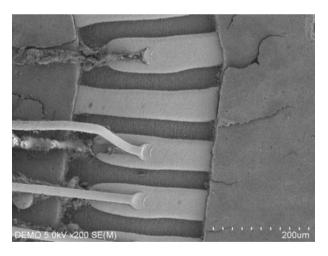

Figure 4.14: Tin whiskers grow out of solder and can get quite long causing leakage and shorting issues. Image by EAG.

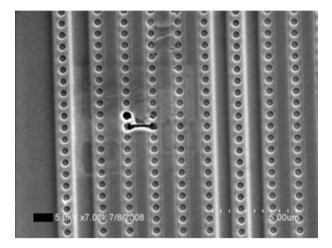

Tin whiskers can grow out of tin containing solder, an example of which is shown in Figure 4.14. Usually, strain is the driving force and the whiskers can grow quite large and cause shorting or leakage issues in a device. A large amount of effort has been made to understand and eliminate the conditions for whisker growth.

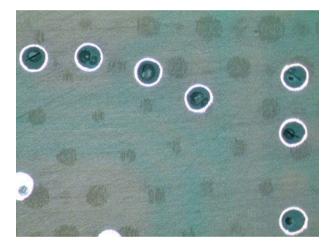

Dendritic growth can occur with silver or copper under the right conditions. I have only ever seen dendrite from field returns and biased damp heat reliability testings. The potential directs the growth and the humidity works with some ions (typically Cl) to etch one copper trace or the silver epoxy die attach and moves the metal toward the nearest ground or negative bias spot. This grows dendrites or halos which will eventually result in leakage and shorts. An example of dendritic growth in shown in Figure 4.15.

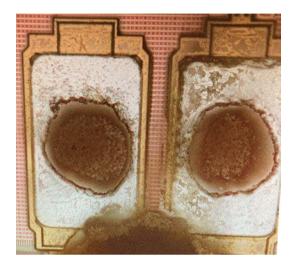

Corrosion can happen when the etchants used in the FAB process are not completely removed (typically Cl and F). An example of a corrosion is shown in Figure 4.16. These can corrode the Al pad and the IML. This is easy to see once the part is decapped, but finding the culprit (Cl, F, or another etchant) is difficult as the decap process will wash them away. This requires a dry-etch approach which typically takes longer and requires a higher level of skill.

Truly bad or unlucky assembly houses also create issues by not properly cleaning the die and package components prior to assembly and the contamination present will cause opens and high resistance by interfering in the bonding process. Also, faulty tools or clumsy operators can cause wire sweep and allow stray material (typically wires or solder) to fall onto the die surface leading to shorts. Occasionally even finger prints have been found on die which are excellent sources for Na, K, and Cl all of which do bad things to devices. Having a good assembly house is a very big deal.

One assembly house I dealt with had developed a cleaning process involving plasma on the die and the copper lead frames. They did all the work with a single lead frame at a time. When they had the process set, they the loading 120 lead frames and were surprised to get many bonding failures. It turns out that the lead

Figure 4.15: Ag dendrites on a sensor board. EDX identifies the dendrites as Ag. Image by EAG.

Figure 4.16: Corrosion on bond pads. The brown areas in the bond pad squares are where the Al has been etched away. Image by EAG.

frames in the center of the plasma tool were shielded very nicely by the surrounding lead frames, so about 40% were not cleaned at all.

Of course, there are many other defects found, but we cannot cover them all in just one book. Each year there is a very good conference, known as International Symposium on Test and Failure Analysis (ISTFA), on FA that has several papers covering examples of FA work on specific types of defects.

#### **Chapter 5**

#### Destructive versus nondestructive analysis

In approaching failure analysis work, it is always best to have a plan before touching a part. The steps of the plan are followed and choices made after each result is obtained. The problem with a locked in plan for FA is that after each step, the results determine what the best next step is and sometimes there are several options that make sense. A plan with multiple branches and some question marks is what we typically have in FA.

The first steps should always be the nondestructive analyses and verification tests for the suspected failure mode. These leave the sample basically unchanged. Nondestructive testing (NDT) is not always completely without effect on the parts but is usually so. The most common exceptions are that X-rays can affect very vulnerable memory; in the DI water, the part which must be submerged in for C-SAM can cause electrical leakage and some materials that are water soluble may be removed. But the most common issues are with handling: dropped samples can be damaged, ESD events can occur if the proper precautions are not taken, and even improper placement in carry devices can damage the samples. This is part of why it is always desirable to have multiple samples, but this is not always possible.

The order of analysis may be changed depending on the exact failure mode, but normally proceeds in this order: Optical inspection, electrical verification of the failure mode, X-ray to see if any wire bond or solder issues are obvious, and then C-SAM to check for delamination on the die or wire bond area, or in the case of flip chip devices delamination in the die or at the underfill interfaces. An example of a failure observed in C-SAM is show in Figure 5.1.

The electrical verification of the failure mode is very important as the parts can recover or incorrect parts may have been submitted. If the failure mode is gone it is very difficult to find the root cause of an issue that is not there. You do not want to spend your valuable time chasing nonsense. If the wrong parts were sent, then the right ones can be sent. If the part(s) recover that actually points to likely issues. Leakage due to water in the part or dendritic growth in the parts can both recover over time or with a bake. Many labs actually do a quick 12 h bake at 100 °C before continuing on with an FA to ensure they are not chasing these failure modes in the lab. The dendritic growth can sometimes be caught by p-lapping or plasma removal of the encapsulant to reveal the die without removing the delicate dendritic growth. If you know that you are looking for dendrites you have a chance but with water ingression you never find directly only through indirect evidence. Placing the recovered part in a damp heat chamber or submerging the device in water for at least 4 h to check if the failure mode returns for instance.

Other less common NDT methods used in FA include: time domain reflectometry (TDR), IR (infrared) imaging, and FTIR (Fourier transform infrared Spectroscopy).

**Figure 5.1:** Reflection mode C-SAM image of bonded wafers with air gaps between the wafers (white areas). Image by Lisa Logan.

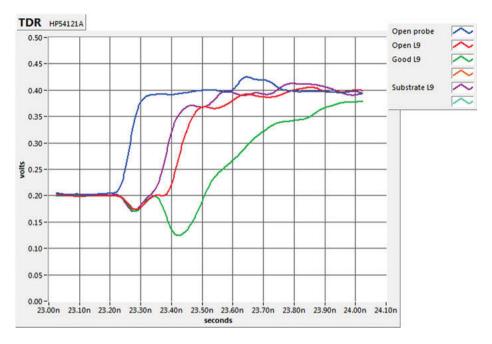

TDR uses a probe setup to contact the pin or solder ball in question and an adjacent ground. A pulse of electrons is sent into the sample and the reflected signal is captured. At each interface in the path of the electron pulse, a portion of the signal is reflected. So, the solder ball to the pad, each interface in the bond pad, the vias connecting each trace to the next level in the substrate (top and bottom of each via), onwards to the bond wire (or solder bump for flip chips), and then into the die. So, usually about 10–30 interfaces. This produces a squiggly line for a device probed at a particular input. Some people claim they can tell what each turn in the line indicates and its location in the device. I find this hard to believe. Fortunately, this special power is not required to understand the analysis.

Using the failed unit (FU), a known good part (KG), and a good substrate (GS), a comparison can be made and the location in the spectrum that the failed part deviates from the KG or GS signal provides the general location of the defect. If it is before the GS overlap with the KG then the defect is in the substrate. If the deviation occurs just at or just after GS then the defect is at the interconnect (bond wire or solder bump) and if the deviation is further in, then the issue is in the die. Now if the signal does not deviate from the KG then breathe and recheck your setup as you are either testing the wrong part, the wrong pin, or the part has recovered.

The preparation of a GS if one is not available from the customer is straight forward if you have an additional KG device. Simply grind/polish the part to break the bond wires or remove the die for flip chip devices. This should be a quick 10-min operation at most.

TDR is what I call the unparalyzing tool. I have experienced a meeting in which discussion of what to do for the only failing part in a qualification for a major customer took the following horrible path. The device fails and does not recover. There is no obvious physical damage. We need to show root cause of failure or the customer will walk away. Ok, can we decap to examine the die – no the failure might be on the die surface. Ok, can we remove the substrate and examine the die through backside analyses - no, the issue could be in the substrate. Ok, can we break the bond wires and electrically check both sides - no, the issue could be between the bond wires. So, we can just look at the device intently and wait. We are paralyzed.

The TDR makes this problem go away and we can identify the region of the issue and start to do the destructive FA. This also lets people know which, the substrate, assembly, and die, has the issue and they can go and starting examining the issue in the right place.

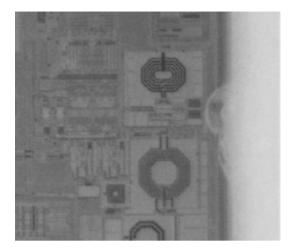

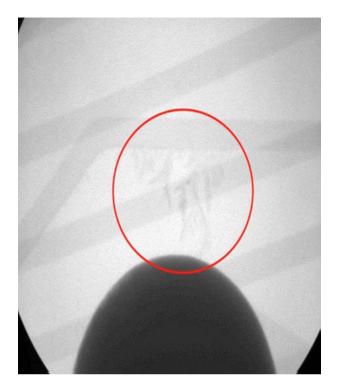

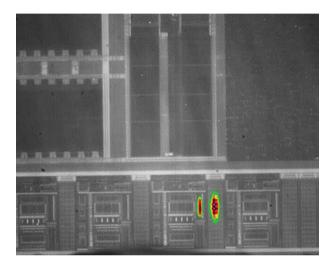

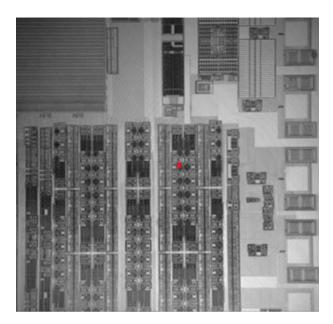

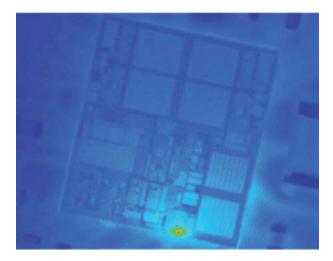

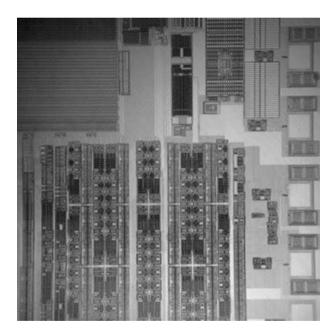

IR imaging is used to look through silicon to examine the circuitry in a die. Typical use is to examine a flip chip device for defects and cracks, especially at the corners or scallops along the edges of the die. The technique is fairly quick but is usually on an expensive instrument. The defects found in this way commonly result from dicing operations. Normally there is some roughness on the sides of the die after dicing, but any damage that extends past the end of the street and into the circuitry is an issue. The damage may cause immediate failure or create a reliability issue as the cracks may increase in size over time.

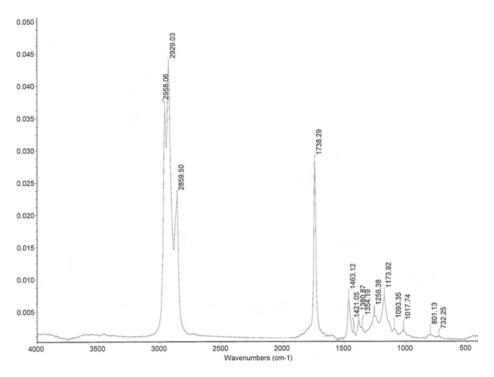

Fourier transform infrared spectroscopy (FTIR) is a tool used to identify organic materials [1]. When a sample in an FA has a grease or oil or stain that appears to be organic in nature, then FTIR can be employed to identify the material. FTIR instruments come in two main varieties: low cost with a large sample area needed or one with a microscope which can look at a small spot of ~15 microns. The IR does need a healthy, 50-nm-thick analysis depth. So, very thin contamination areas cannot be analyzed. The use of attenuated total reflection (ATR) can make the analysis more surface sensitive as the IR beam is passed through the surface layer many times to increase the absorption by the contaminant. The spectra collected from the FTIR work should have a blank spectrum subtracted from it to remove the peaks present from the air.

To determine what materials are present, the spectra can be examined and each peak or set of peaks can be assigned to a particular functional group: OH, CH<sub>2</sub>, and so on. An easier way is to use libraries of spectra that are commercially available to match to the acquired spectrum. There are large libraries of spectra from known materials with hundreds of thousands of spectra available, and of course the labs can add any spectra they have done themselves. In this way, very quickly, a best match can be obtained for the unknown contamination.

A good practice in a fab support FA lab is to collect all the known materials being used in the fab and create a spectrum for each to be used in their library searches. If the bandwidth is available, the materials can also be exposed to heat and UV to get the spectra for the degraded versions as well.

There are many other materials analysis techniques that can be used in FA work, but these are less common. Doing some research in the literature or contacting a service lab will help determine the best course of action when these less common techniques are required.

## Chapter 6 Optical Microscopy (OM)

Typically, every FA group has at the very least an optical microscope. Most will have two with a camera for capturing the images. The two scopes are usually a low magnification scope, 20–200x, which is trinocular, two tubes for your eyes and a third above for the camera mount. The higher magnification microscopes have many variants; from the low-cost versions with five or so optical choices ranging from 5 to 150x and a 2–20x increase in magnification for the rest of the system. So, the final magnifications are generally 10 to 3,000x. The highest magnification lenses often require immersion and I avoid these as they are messy, have very short focal lengths, and can introduce surface contamination from the immersion fluid. Just use the SEM at that point.

There are straight bright field microscopes, although the high magnification scope can have dark field optics as an option for some of the magnifications, this is usually a decision made based on cost. Having one dark field optic is a great option for those cases when bright field does not provide the right contrast. The low-cost "Dan Sullivan" version (I was told of this package by a vendor after I had bought this set up for the third time): A low magnification scope (20–150x) and a higher magnification scope with five objectives of which only the 10x optic was bright and dark field. These two scopes share a single 3 MP camera and one computer with capture and image processing software.

If money is not an issue, then many alternative optical microscope varieties are available for FA. Many scopes now have bright field and dark field along with mixing and angle options. These enable shading and very surface-sensitive images to be obtained. A motorized stage is very helpful for calibrated measurements as well as enabling multiple images to be taken across the sample which are stitched together by the software to make a large area image at maximum magnification and resolution. This is a great time saver and stops the endless requests for "just one more image here at higher resolution." Large die, 16 mm square or larger, can be imaged at maximum magnification and resolution and presented as one image. If the customer wants to zoom in on an area they can and the resolution is already the best it can be on that system. These scopes are about three to four times the cost of the special.

Also available at the higher end are confocal microscopes which have very narrow focal planes so different layers in a sample can be observed. This in theory removes the need to then delayer the samples to determine which layer the issue is on. I have yet to have a customer accept this and have always had to do the follow up delayering or cross section to image the defect directly.

Additionally, at the high end are the infinite focus scopes that allow a continuous changing of the magnification instead of the step magnification provided by

multiple optics scopes. These are very nice in that the area of interest can be zoomed in to include whatever is desired instead of a shot at 5x in which the defect is very small and then the next step, 10x, magnification in which the defect more than fills the screen.

Some systems have autofocus features which can be used to get all layers in the images to be in focus in the captured image. The same feature can provide Z measurements and easily determine if features are boulders or divots which can be difficult to determine from just a top-down image.

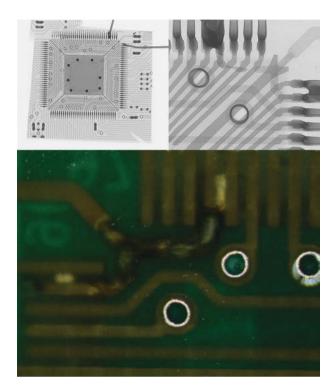

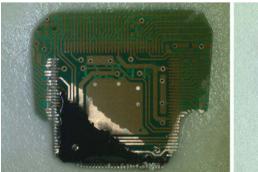

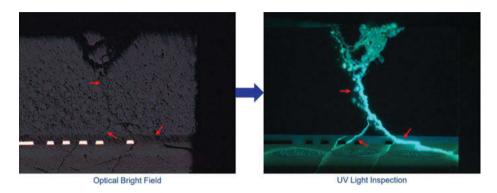

Shown in Figure 6.1 are images of PCB damage with bright field, dark field, and dark field with the sample covered in IPA. The dark field with IPA allows clearer imaging of the buried metal trace. One of the advantages of optical imaging is that some materials can be seen through as is obvious in the images of the PCB. The limiting factor of optical microscopy is the magnification/resolution possible. Without considering laser imaging, the maximum magnification is ~2,500x. With immersion lenses and some tricks, it can be slightly higher. This is good, but often insufficient for FA on modern electronics/semiconductor devices.

**Figure 6.1:** Optical images of PCB damage with bright field, dark field, dry and covered with isopropyl alcohol (IPA). The IPA fills in the scratches on the surface and allows clearer imaging of the buried layers. Image by EAG.

The use of optical images for documenting samples and inspections should be universal. If you set up a general FA SOP, it should always have step 1: Take optical images of the sample(s). If there are multiple samples, then take an image of a normal sample and any deviant devices as well.

Unfortunately, many labs use the optical microscope for initial inspection, but do not save the images. This is counter-productive as these images make it much easier to understand a report, visualize what the sample is, the locations of analysis/defects,

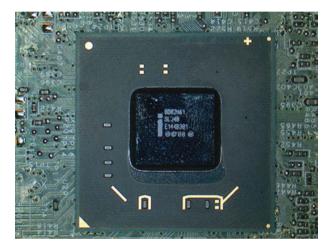

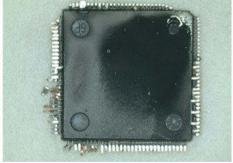

capture the condition of the sample when received, and after certain operations are performed on the sample. These often seem obvious to the direct customer and the analyst, but a few weeks later when the VP of the major customer wants an explanation in detail these images are very helpful. Explaining that the samples looked worn and not quite right is helpful, but an image showing the condition will speak for itself. Electronic images are free, take many. A great many times I have received a call after completing an FA with a request for the date code or part number of the device. These are almost always found on the device itself, but after an FA the device has been decapped or worse and the printed information is no longer present. A couple of images of the as-received part(s) solves all these requests, such as the image in Figure 6.2.

Figure 6.2: As-received device on a PCB. Note that the information on the device in the image allows for retention of information will be lost during the FA process. Image by Dan Sullivan.

In some cases, the optical images may be all that is needed to wrap up an FA. The missing solder ball, the huge crack in the package, and the fact that the part is completely burnt or not the right device all close the FA book. Large EOS damage captured by the OM such as the example shown in Figure 6.3, also falls on the done list.

A special note here on naming data files. This will be true for all data files and I mention it here as Optical images are generally the first collected.

For the naming of files, any scheme you wish to use that is consistent should work. I have adopted the following when possible: the job number is month (03), day (15), and year (2022) for the ides of March this year and then a number 01. So, the third job to come in today would be 0315202203. This is the name of the top folder for this FA. The images I then separate into folders for each type of work (optical, SEM,

Figure 6.3: Optical image of some Electrical Overstress (EOS) damage in a die. Image by EAG.

etc.) The images get named with the job number, sample ID, and then a 1, 2, 3, and so on. This seems like a lot of work, but it makes finding items later much easier, especially for someone other than the analyst that did the work. You will be much happier with a good system when you have to answer a customer about work from two months ago done by Johnny who is on vacation.

# Chapter 7 Scanning Acoustic Microscopy/Tomography (SAM or SAT)

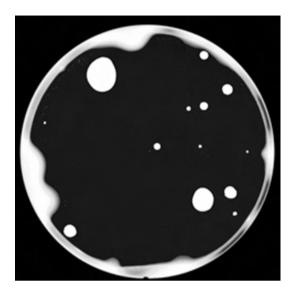

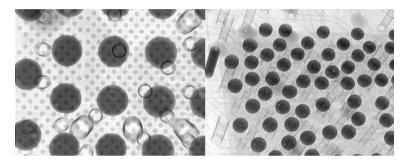

This nondestructive technique uses sound waves to scan a sample. The reflected and transmitted signals are captured and images of the interfaces selected are created. The samples need to be submersed in a liquid medium for analysis. Normally, DI water is used. Other liquids may be used like IPA but the smell, cost, and evaporation rates make water the most often used. C-SAM instruments are essentially fancy air bubble detectors. The speed of sound is very different in liquids and solids compared to air. This large difference results in a very high reflection percentage at air interfaces. Thus, air gaps result in very bright areas in reflection images and very dark ones in transmission or thru scan images. Samples must be fairly flat with surfaces that are not too rough; otherwise, the sound waves will be reflected away from the detector and no signal will be observed.

The resolution in X and Y dimensions depends on the material scanned and the transducer frequency but is typically no better than 15 microns, while in the Z dimension it is very thin, ~0.01 micron air gaps can be detected. The higher the frequency of the transducer, the better the XY resolution. However, as the higher frequency signal is more readily absorbed by materials, this reduces the depth of penetration into the sample. So, thick samples are not as readily analyzed by the higher frequencies.

The transducers are made with different focal points and this also affects the thickness of samples and the width of the focal plane (Z resolution). Since each transducer is between \$500 and \$12,000 USD today, having a complete set can get very expensive. Typical FA sets include 10, 20, 30, 50, 100, and 150 (230) MHz. Different instrument manufacturers use slightly different numbers but this set is common. For examination of smaller devices, a few mm square, a 75 or 90 MHz are often added.

To examine typical IC packaged devices, 30 and 50 MHZ are the most commonly used. For flip chip (FC), the heat spreader is attached to the substrate by adhesive and by thermal grease so the die can be analyzed as received with the same transducers. But if the substrate/underfill and die/underfill interfaces or internal layers in the die itself are of interest then the heat spreader needs to be removed and any adhesive on the die cleaned off. The 100 or 150 (230) MHz transducers are used when analyzing the FC die and underfill interfaces depending on the thickness of the die.

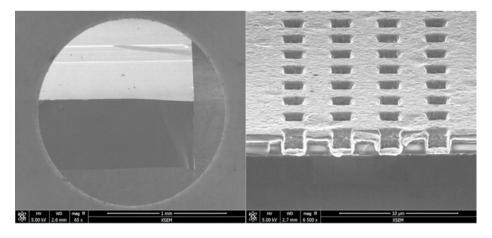

Removal of the heat spreader varies from very easy using a razor blade or modified wafer tweezer in a few minutes to soaking overnight in solvent, or polishing/chemically etching away the heat spreader. Using the cut and pry method on the tougher samples usually results in cracking and shattering the die. The polishing

method always works but takes the longest and requires some training/skill. The heat spreader is not completely removed by polishing but instead when it is thin enough, it can be peeled off. This method ensures no accidental grinding on the die occurs. Once the heat spreader is removed, there is almost always some greyish material on the die. This is either thermal grease or a thermal epoxy of some sort. Its function is the transfer of heat from the die to the heat spreader and lends some structural integrity to the device. The thermal grease is usually easily removed by a cotton swab with IPA and elbow grease.

Sometimes, the thermal grease is dried out or the thermal epoxy is tough. This requires some force and scrapping of the material to remove it. Do not use metal tweezers to do this removal. Best case is when you are so skilled it works, but usually it will crack or badly scratch the die. Use a wooden tool, a broken cotton swab stick works well. The wood is not hard enough to damage the die and will remove the material with some work and IPA. If the material is not removed it will show up in the C-SAM images as it absorbs or scatters some of the signal. Figure 7.1 shows optical images of devices at varying degrees of material removed.

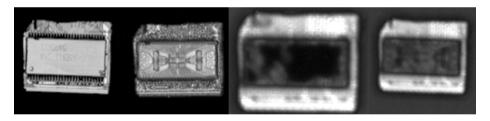

Figure 7.1: Optical images of a FC device with heat spreader (HS), HS removed, and thermal attach cleaned off. Image by EAG.

**Figure 7.2:** C-SAM images of FC device with set Z, scanned with images at three depths: Die to bumps, bumps alone, and bumps to substrate. Image by EAG.

The most common use for the C-SAM is in reliability studies to examine all the samples prior to stress and after stress, sometimes at intermediate points along the test timeline. JEDEC Specification 883 calls out the pass/fail criteria used. All reliability testing uses of C-SAM on ICs follow these guidelines when looking for failures. Delamination may not be present on the die surface or any wire bonding surface. Delamination may not grow during the testing or go from one edge of the device to another edge.

In FA, these same guidelines generally apply. If there is a suspected delamination observed in an active area that is always bad; in other areas it depends. C-SAM is usually not the last step in any FA. It is more of a technique to call out that something is wrong and should be further probed. It may be acceptable to call out delamination directly from C-SAM images. Before an anomalous area on a C-SAM image is designated as delamination, there should be a solid history of cross section confirmed cases on the same type of part. An example of such delamination is shown in Figure 7.3.

Figure 7.3: C-SAM image of underfill delaminating in a Flip Chip device. Image by EAG.

This is a technique that needs an experienced and honest operator. It is fairly easy to make good samples look like total failures and vice versa. Samples with some delamination, but not total delamination, are harder to disguise, but it can be and I have seen it done.

I once worked at a company where I took over a very dysfunctional lab. In reviewing the older data, I asked if all the old data can be thrown away or do I need to start calling past customers to inform them that their passing parts really failed. In these old jobs, the focus was not right and the contrast was lowered along with the gain so everything was washed out, but I could still see the delamination areas. The technicians, both of whom were gone within 30 days of my arrival, did not understand the physics of the technique and just tried to make the images match older images in any way they could. Part of this was fear of results showing failure and part was because they did not understand what they were doing and the repercussions of what they were doing. Trained staff that are encouraged to always tell the truth no matter the consequence is very important to any lab, but especially in FA where unpopular results occur and the staff have to be aligned to the truth and no other line of thinking or they cannot be trusted, especially with techniques like C-SAM where the result can be faked by very skilled or very unskilled operators.

I have been asked many times by people who have sent me C-SAM data they got elsewhere if the delamination they see in red is real or not. If they send me only the reflected scan image with the red/yellow/gray scale, I tell them they have a very nice picture that their child could have drawn for them, but it means nothing. The reflected scan only, especially the red/yellow/grey one is useless unless you know the source and trust it. You really want the Thru scan and a couple of A scans (in a good versus delamination area) to verify the results. If your FA provider is unwilling to provide a couple of A scans then you should run from them as fast as you can. They either do not know what they are doing or worse they do and are not to be trusted.

**Figure 7.4:** C-SAM results for the top surface of the device, die surface scan, and then Thru scan with air trapped between the device and the PCB, with the air bubble removed. Image by EAG.

The next consideration for C-SAM is that the samples need to go into liquid, most often DI water. Typical DI water is 15 M Ohms out of the bottle and after a couple of days in the tank is about 2–3 M Ohms. The water should be changed every week at the longest or things start to grow. To impede the growth, I have used IPA and Listerine in 20 mL doses once a week to help delay the algae bloom.

The samples have to be able to survive the DI water, so no sugar cookies samples. Bubbles on the samples are an issue as they appear as round air gaps. For parts that do not have leads going into the packages, an IPA dip can be used to reduce the surface tension and prevent bubble formation. A simple squeeze bottle of DI water can be used to spray the submerged samples to dislodge bubbles as was

done in the Figure above to dislodge the air trapped between the device and the PCB below. So, a couple of scans may be needed to ensure all bubbles are removed before saving the final data.

I have been asked which is better C-SAM or X-ray and the answer, which is a common answer in FA, is that it depends. We will go over X-ray in FA in the next chapter, but the short answer is that C-SAM is great for flat samples, that have a very thin air gap (Z > 0.01 microns) and is greater than 15 microns in diameter (X and Y) while X-ray is great for samples that have a significant change in density (1 micron solder particles where they should not be in a polymer for example). The two techniques are complementary and both have instances where they are the clearly superior choice in detecting certain types of defects.

The range in samples for commercially available C-SAM systems are small LEDs or ICs of 1 mm<sup>2</sup> up to 300 mm wafers and even 25-inch diameter shower heads that are four inches tall in the larger systems. Beyond these, specialty systems can be made for larger samples, odd shapes, and I have even heard of systems that rotate the sample in sync with the scans, to examine car tires for instance.

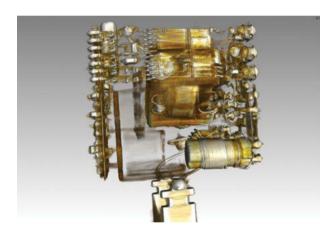

### Chapter 8 X-ray imaging (2D and 3D)

X-ray imaging has several variants. Commonly in an FA lab, there is a 2D capability to quickly and nondestructively image a device to check for stray solder, broken wires, and obvious flaws in the interior of a device. The additional capability of 3D or CT (computed tomography) is growing more common. This enables devices to be imaged at many angles, usually every half a degree in rotation through 360 degrees, and then these images go through a software breakdown which enables the reconstruction of slices of the sample to be created. This typically has lower resolution than the 2D images by a factor of 7–30 but provides the slices without the interference of the rest of the sample. Something on the order of 700 slices are created in each orthogonal direction: front to back, top to bottom, and right to left. Each of these slices may be examined individually which removes the issue of having to look at the entire sample and getting interference from material above and below the area of interest.

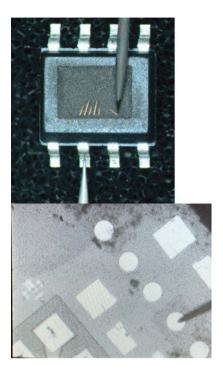

Initially, when 3D X-ray became available as an analytical technique, I was very skeptical. In the vast majority of work, I would use the better resolution of 2D and avoid the long analysis times and added expense of the 3D analysis. Then, I had an issue with woven wire mesh and the 3D provided the answer when 2D could not hope to show the defect. The majority of issues are still more easily and quickly done by 2D but the 3D capabilities have proven that there is a place where it is the best option to provide the evidence of failure.