## MACHINE LEARNING FOR SEMICONDUCTOR MATERIALS

Edited by Neeraj Gupta, Rashmi Gupta, Rekha Yadav, Sandeep Dhariwal and Rajkumar Sarma

# Machine Learning for Semiconductor Materials

Machine Learning for Semiconductor Materials studies recent techniques and methods of machine learning to mitigate the use of technology computer-aided design (TCAD). It provides various algorithms of machine learning, such as regression, decision tree, support vector machine, K-means clustering and so forth. This book also highlights semiconductor materials and their uses in multi-gate devices and the analog and radio-frequency (RF) behaviours of semiconductor devices with different materials.

#### Features:

- Focuses on semiconductor materials and the use of machine learning to facilitate understanding and decision-making.

- Covers RF and noise analysis to formulate the frequency behaviour of semiconductor devices at high frequency.

- Explores pertinent biomolecule detection methods.

- Reviews recent methods in the field of machine learning for semiconductor materials with real-life applications.

- Examines the limitations of existing semiconductor materials and steps to overcome the limitations of existing TCAD software.

This book is aimed at researchers and graduate students in semiconductor materials, machine learning and electrical engineering.

**Neeraj Gupta** is an Associate Professor at Amity University Haryana with over 16 years of teaching experience. His expertise includes VLSI design, low-power and analog design, AI and embedded systems. He has published 40+ papers, two book chapters, one book and 12 patents, and has received the Best Researcher and Best Teacher Award (2024).

**Rashmi Gupta** is an Assistant Professor at Amity University Haryana with 13+ years of experience. Her research interests include AI, software engineering and IoT. She has authored 20+ papers, two book chapters, one book and five patents.

**Rekha Yadav** is an Assistant Professor at DCRUST, Murthal. She specializes in semiconductor device modeling and VLSI design with 15 years of experience, over 30 publications and four book chapters.

**Sandeep Dhariwal** is an Associate Professor at Alliance University, Bengaluru. With 14+ years of experience, he focuses on low-power CMOS and semiconductor modeling. He has published 40+ articles, three books and holds three patents.

**Rajkumar Sarma** is a Postdoctoral Researcher at the University of Limerick, Ireland. With 11+ years of experience, his research spans digital VLSI, FPGA prototyping and quantum architectures. He has 25+ publications, 15+ patents and two books.

#### **Emerging Materials and Technologies**

Series Editor: Boris I. Kharissov

The *Emerging Materials and Technologies* series is devoted to highlighting publications centered on emerging advanced materials and novel technologies. Attention is paid to those newly discovered or applied materials with potential to solve pressing societal problems and improve quality of life, corresponding to environmental protection, medicine, communications, energy, transportation, advanced manufacturing, and related areas.

The series takes into account that, under present strong demands for energy, material, and cost savings, as well as heavy contamination problems and worldwide pandemic conditions, the area of emerging materials and related scalable technologies is a highly interdisciplinary field, with the need for researchers, professionals, and academics across the spectrum of engineering and technological disciplines. The main objective of this book series is to attract more attention to these materials and technologies and invite conversation among the international R&D community.

#### **Solar Cells Development and Fabrication**

Edited by Shivani Dhall, Kapil Sood and Vinay Gupta

#### Geopolymers and Composites: Processing Technologies and Applications

Edited by Huirong Le, Kaibao Wang and Longyuan Li

#### **Nanomaterials for Electrochemical Sensing**

Edited by Syed Shahabuddin, Rama Gaur and Nandini Mukherjee

## Organic-Inorganic Hybrid Nanomaterials: Energy Harvesting, Storage, and Advanced Applications

Edited by Srikanta Moharana, Bibhuti B. Sahu and Suresh Sagadevan

## Nanocarbon to Polymer-Nanocarbon Composites: From Synthesis to Breakthrough Performance

Edited by Srikanta Moharana, Bibhuti B. Sahu and Suresh Sagadevan

#### **Materials for Dye Degradation**

Edited by Tarun Parangi and Soyebkhan Pathan

#### Circularity of Cementitious Materials: A Practical Approach

Christian Paglia

#### **Machine Learning for Semiconductor Materials**

Edited by Neeraj Gupta, Rashmi Gupta, Rekha Yadav, Sandeep Dhariwal and Rajkumar Sarma

For more information about this series, please visit: www.routledge.com/Emerging-Materials-and-Technologies/book-series/CRCEMT

## Machine Learning for Semiconductor Materials

Edited by Neeraj Gupta, Rashmi Gupta, Rekha Yadav, Sandeep Dhariwal and Rajkumar Sarma

Designed cover image: Shutterstock

First edition published 2026 by CRC Press

2385 NW Executive Center Drive, Suite 320, Boca Raton FL 33431

and by CRC Press

4 Park Square, Milton Park, Abingdon, Oxon, OX14 4RN

CRC Press is an imprint of Taylor & Francis Group, LLC

© 2026 selection and editorial matter, Neeraj Gupta, Rashmi Gupta, Rekha Yadav, Sandeep Dhariwal and Rajkumar Sarma; individual chapters, the contributors

Reasonable efforts have been made to publish reliable data and information, but the authors and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, access www. copyright.com or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978–750–8400. For works that are not available on CCC please contact mpkbookspermissions@tandf.co.uk

*Trademark notice*: Product or corporate names may be trademarks or registered trademarks and are used only for identification and explanation without intent to infringe.

ISBN: 978-1-032-79688-8 (hbk) ISBN: 978-1-032-83215-9 (pbk) ISBN: 978-1-003-50830-4 (ebk) DOI: 10.1201/9781003508304

Typeset in Times by Apex CoVantage, LLC

## Contents

| Editor Biogr<br>List of Cont | ix raphies xi ributors xiii                                                                                  |

|------------------------------|--------------------------------------------------------------------------------------------------------------|

| List of Figur                | res and Tablesxv                                                                                             |

| Chapter 1                    | Semiconductor Materials: Current Applications and<br>Limitations of Advanced Semiconductor Devices           |

|                              | C. Shekhar                                                                                                   |

| Chapter 2                    | Machine Learning: Introduction and Features                                                                  |

|                              | Deborah T. Joy, Raygun Jose, Charu Jain, Divia T. Joy<br>and Rashmi Gupta                                    |

| Chapter 3                    | Fault Detection in Semiconductor Manufacturing: A Classification Analysis of the SECOM Dataset               |

|                              | Vanshika Jain, Rashmi Gupta, Neeraj Gupta and Prashant Kumar                                                 |

| Chapter 4                    | Predictive Modelling for Yield Enhancement                                                                   |

|                              | Arpita Pattnaik, Neeraj Gupta, Rashmi Gupta, Arun Kumar Singh<br>and Rajkumar Sarma                          |

| Chapter 5                    | Deep Learning for Image Classification in Semiconductor Inspection                                           |

|                              | Vanshika Jain, Rashmi Gupta, Neeraj Gupta, Prashant Kumar<br>and Rajat Butola                                |

| Chapter 6                    | Machine Learning for Semiconductor Devices                                                                   |

|                              | Nivedita Manohar Mathkunti and Manjulata Badi                                                                |

| Chapter 7                    | Numerical Simulation-Based Biosensing Performance Exploration of a Cylindrical BioFET Using Machine Learning |

|                              | Amit Das, Sonam Rewari, Binod Kumar Kanaujia, S. S. Deswal and R. S. Gupta                                   |

viii Contents

| Chapter 8  | Semiconductor Materials for EV and Renewable Energy 142                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Manjulata Badi and Ila Rai                                                                                                                                   |

| Chapter 9  | Performance Comparison of Vertical TFET Using Triple Metal Gate Structures and Insights of Machine Learning Approach: A Comprehensive Study                  |

|            | Neharika Sharma, Neeraj Gupta, Karamjit Kaur Sekhon and<br>Seema Narwal                                                                                      |

| Chapter 10 | Design and Performance Exploration of Macaroni Channel-Based Ge/Si Interfaced Nanowire FET for Analog and High-Frequency Applications Using Machine Learning |

|            | Aapurva Kaul, Amit Das, Shivani Yadav, Sonam Rewari and<br>Deva Nand                                                                                         |

| Index      | 201                                                                                                                                                          |

## **Preface**

The semiconductor industry has grown very rapidly. The electronic system, which is composed of numerous numbers of transistors, is expected to grow similarly. Unfortunately, transistors suffer from process variation, which also results in varying device performance. Low-power consumption and high-speed applications impose a huge requirement on small-sized devices. So metal oxide semiconductor field effect transistors (MOSFETs) have been scaled to meet the market's future requirements. The scaled MOSFET is more prone to process variation as compared to long-channel devices. These scaled devices suffer from short channel effects (SCEs). The device characteristics must be predicted before its fabrication to prevent failure. Currently, the device characteristics with parameter variations are studied by using technology computer-aided design (TCAD). But a long simulation time is required for good accuracy. Recently, a wide range of machine learning algorithms and techniques have been used in every domain of engineering. This approach provides a better trade-off between time and accuracy for meeting market requirements.

One of the most pressing problems in all domains of engineering is the requirement of advanced materials. Conventional materials have approached their limit and cannot be used in future applications. There are various industrial applications where new and advanced materials can play a vital role. This book presents a journey from present to future materials for semiconductors. TCAD is used for device simulation, but it is costly and time consuming to do simulations on TCAD nowadays. Due to TCAD's limitations with device variation and accuracy, machine learning is replacing TCAD. It provides better accuracy and is a powerful technology in material research.

The book *Machine Learning for Semiconductor Materials* studies recent techniques and methods of machine learning to mitigate the use of TCAD, as the use of TCAD tools in semiconductor devices is very tedious. The utilization of machine learning algorithms for semiconductor devices improves device and process accuracy and helps in the analysis of the process variation of the device. This book presents various machine learning algorithms, such as regression, decision tree, support vector machine and *K*-means clustering. It explores the materials and their applications in various domain of science, technology and everyday life to provide further research on the subject. It also highlights semiconductor materials and their uses in multi-gate devices. It is ideal for physicists, computer specialists, engineers, practitioners, researchers, academicians and students who are looking to learn more about machine learning and semiconductor materials and their applications.

## **Editor Biographies**

Neeraj Gupta is an associate professor at Amity University, Haryana, specializing in device modelling, VLSI design, low-power design, analog design, optimization techniques, AI and machine learning and IoT and embedded systems. Dr Gupta received his doctoral degree at Amity University, Haryana, India, in 2019. He has more than 16 years of teaching experience in different subjects. With extensive experience in both academic and research domains, Dr Gupta has contributed significantly to the fields of VLSI circuits and device simulation. His work often bridges cutting-edge technologies with practical applications, making him a key figure in advancing innovations in semiconductor technologies and AI-driven systems. He has published more than 40 international articles in different reputed SCI/SCOPUS indexed journals, presented at conferences, authored two book chapters, and published a book on microprocessors. He also has five published patents. He also received the 2024 Best Researcher and Best Teacher Award from Wegrow Pvt. Ltd.

**Rashmi Gupta** is an assistant professor at Amity University, Haryana, Gurugram, India. Dr Gupta received her doctoral degree at Amity University, Haryana, India, in 2020. She has more than 13 years of teaching and research experience. Her current research interest is in artificial intelligence, machine learning, software engineering, soft computing, IoT etc. She has published more than 20 international articles in different reputed SCI/SCOPUS journals, two book chapters and a book on software testing. She also has five published patents.

**Rekha Yadav** is an assistant professor at DCR University of Science and Technology, Murthal, India. She received her doctoral degree from DCR University of Science and Technology, Murthal, Haryana, India, in 2018. She has 15 years of teaching and research experience. Her current research interest is in semiconductor device modelling, VLSI design etc. She has published more than 30 international articles in different reputed SCI/SCOPUS journals and four book chapters.

Sandeep Dhariwal is an associate professor at Alliance University, Bengaluru, India. Dr Dhariwal received his doctoral degree at Banasthali University, Rajasthan, India, in 2015. He has more than 14 years of teaching experience in different subjects. His current research interest is in semiconductor device modelling, low-power CMOS, VLSI design etc. He has published more than 40 international articles in different reputed SCI/SCOPUS indexed journals, presented at conferences, and authored three books. He also has three published patents in multidisciplinary areas of research.

**Rajkumar Sarma** received his BE in electronics and communications engineering from Vinayaka Mission's University, Salem, India, in 2008. He received his MTech and PhD from Lovely Professional University, Phagwara, Punjab, in 2012 and 2020, respectively. He has more than 11 years of teaching and research experience. He has been working as a postdoctoral researcher at the University of Limerick, Limerick,

Ireland, under the Automatic Design of Digital Circuits (ADDC) project since September 2022. He is also working on a Science Foundation of Ireland (SFI) funded project to generate VHDL/Verilog code for digital circuit design and apply it to the creation of different IP blocks, specifically FIR and FFT filters. His research interests include (but are not limited to) analog and digital VLSI design, low-power architecture design, quantum cellular automata, prototype development using FPGA etc. He has more than 25 research publications in SCI/Scopus indexed and other reputed journals and has presented at national and international conferences. He has published two books on hardware description language and FPGA prototyping. He also has more than 15 published patents in various engineering fields.

## Contributors

#### Manjulata Badi

Department of Electrical and Electronics Engineering Alliance University Bengaluru, India

#### Rajat Butola

Parallel and Scientific Computing

Laboratory

Electrical Engineering and Computer

Science International Graduate Program

National Yang Ming Chiao Tung

University

Hsinchu, Taiwan

#### **Amit Das**

Department of Electronics and Communication Engineering GLA University Mathura, Uttar Pradesh, India

#### S. S. Deswal

Department of Electrical and Electronics Engineering Maharaja Agrasen Institute of Technology New Delhi, India

#### **Nand Deva**

Department of Electronics and Communication Engineering, Delhi Technological University New Delhi, India

#### R. S. Gupta

Department of Electronics and Communication Engineering Maharaja Agrasen Institute of Technology New Delhi, India

#### Charu Jain

Xebia Academy Global Gurugram, India

#### Vanshika Jain

Department of CSE

Amity School of Engineering and

Technology

Amity University

Haryana, India

#### Raygun Jose

Xebia Academy Global Gurugram, India

#### Deborah T. Joy

Xebia Academy Global, Gurugram, India

#### Divia T. Joy

Department of CSE

Amity School of Engineering and

Technology

Amity University

Haryana, India

## Binod Kumar Kanaujia Department of Electronics

and Communication

Engineering

Dr. B. R. Ambedkar National Institute

of Technology

Jalandhar, India

#### Aapurva Kaul

Department of Electronics and Communication Engineering, Delhi Technological University New Delhi, India xiv Contributors

#### **Prashant Kumar**

Department of Electronics and

Communication Engineering,

J. C. Bose University of Science and

Technology

Faridabad, India

#### Nivedita Manohar Mathkunti

Department of Electrical and Electronics Engineering, Alliance University Bengaluru, India

#### Arpita Pattnaik

Department of CSE Amity School of Engineering and Technology Amity University Haryana, India

#### Ila Rai

Department of Electrical and Electronics Engineering Alliance University Bengaluru, India

#### Sonam Rewari

Department of Electronics and Communication Engineering Delhi Technological University New Delhi, India

#### Rajkumar Sarma

Department of Computer Science and Information Systems University of Limerick Ireland

#### Narwal Seema

Department of ECE Dronacharya College of Engineering Gurugram, India

#### Karamjit Kaur Sekhon

Department of ECE

Amity School of Engineering and

Technology

Amity University

Haryana, India

#### Neharika Sharma

Department of ECE

Amity School of Engineering and

Technology

Amity University

Haryana, India

#### C. Shekhar

Department of Physics Amity School of Applied Sciences Amity University Haryana, India

#### **Arun Kumar Singh**

Department of CSE Amity School of Engineering and Technology Amity University Haryana, India

#### Shivani Yadav

Department of Electronics & Communication Engineering KIET Group of Institutions Ghaziabad, Uttar Pradesh, India

## List of Figures and Tables

| Figur | es                                                                |     |

|-------|-------------------------------------------------------------------|-----|

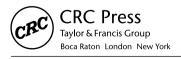

| 2.1   | Artificial intelligence as the superset of learning               | 18  |

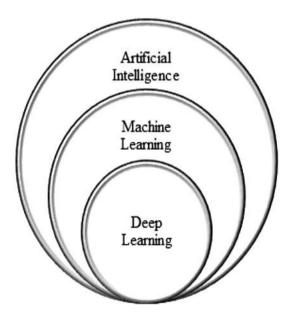

| 2.2   | The AI to ML timeline                                             | 20  |

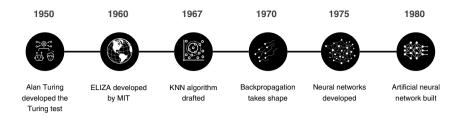

| 2.3   | Machine learning subdivisions                                     | 22  |

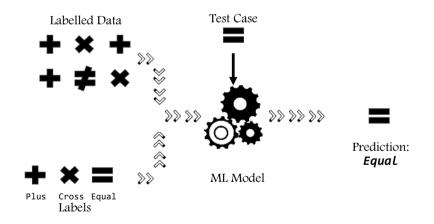

| 2.4   | Supervised learning model                                         | 22  |

| 2.5   | Unsupervised learning logical model                               | 23  |

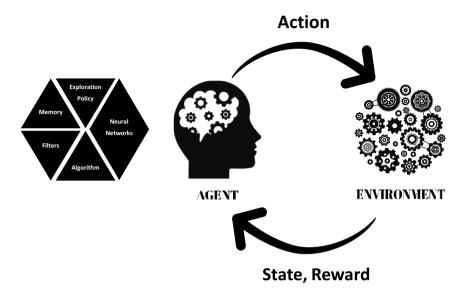

| 2.6   | Representation of reinforcement learning                          | 24  |

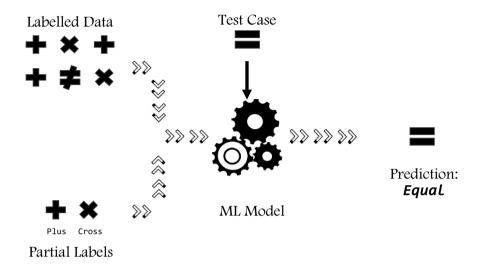

| 2.7   | Sample of semi-supervised learning                                | 25  |

| 2.8   | Accuracy for linear regression                                    | 27  |

| 2.9   | Confusion matrix for logistic regression                          | 28  |

| 2.10  | Accuracy for decision tree classifier                             | 29  |

| 2.11  | Confusion matrix for random forest classifier                     | 30  |

| 2.12  | Confusion matrix for support vector machine                       | 31  |

| 2.13  | Confusion matrix for <i>K</i> -nearest neighbours                 | 32  |

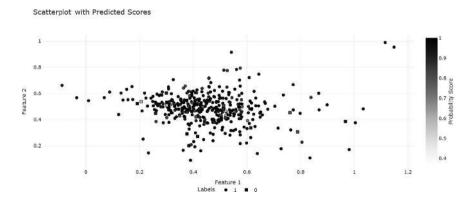

| 2.14  | KNN map for predictions by the model                              | 32  |

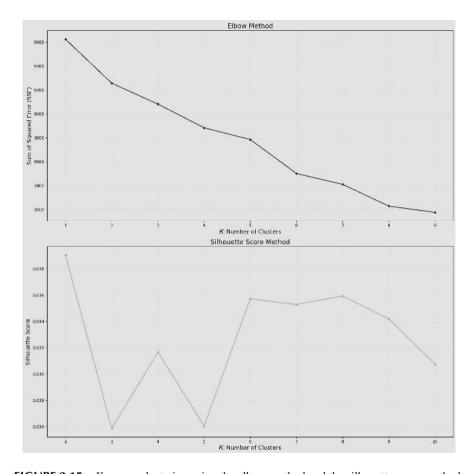

| 2.15  | K-means clustering using the elbow method and the silhouette      |     |

|       | score method                                                      | 34  |

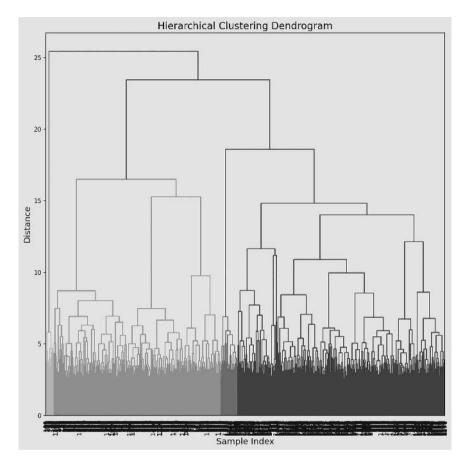

| 2.16  | Hierarchical clustering dendrogram                                | 35  |

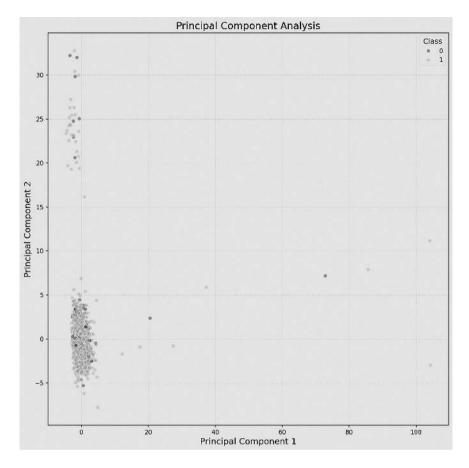

| 2.17  | Principal component analysis                                      | 36  |

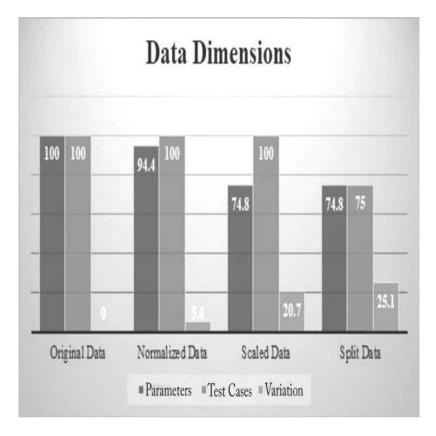

| 2.18  | Dimensions of data over preprocessing                             | 37  |

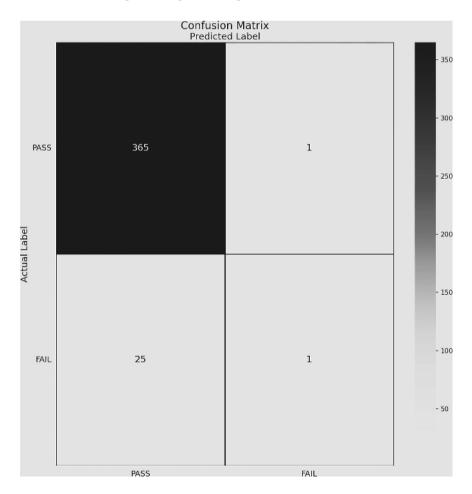

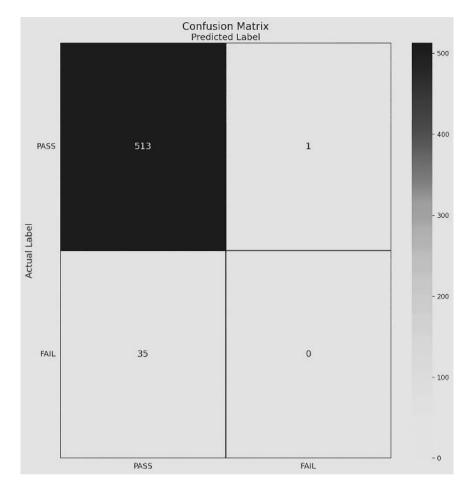

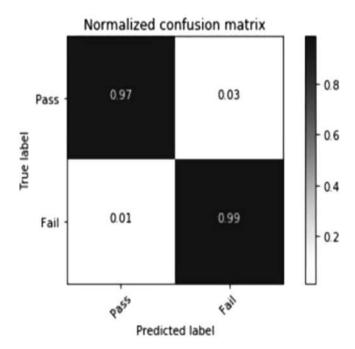

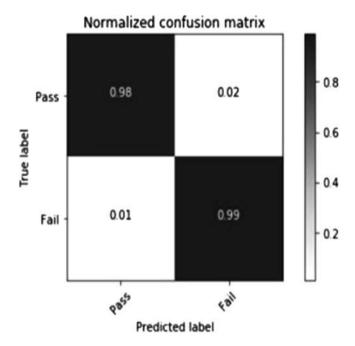

| 3.1   | Normalized confusion matrix for SVC feature selection with        |     |

|       | random forest classification                                      | 52  |

| 3.2   | Normalized confusion matrix for logistic feature selection with   |     |

|       | random forest classification                                      | 53  |

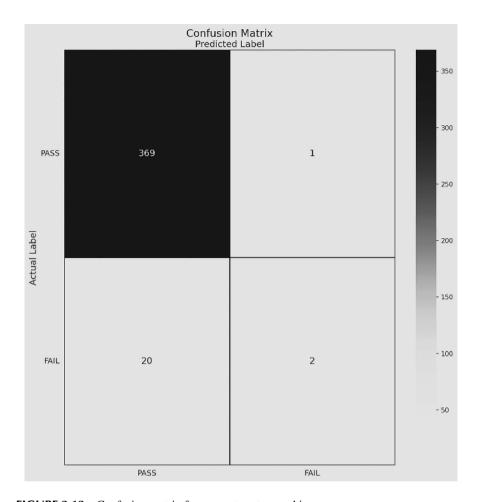

| 3.3   | Normalized confusion matrix for decision tree feature selection   |     |

|       | with random forest classification                                 | 54  |

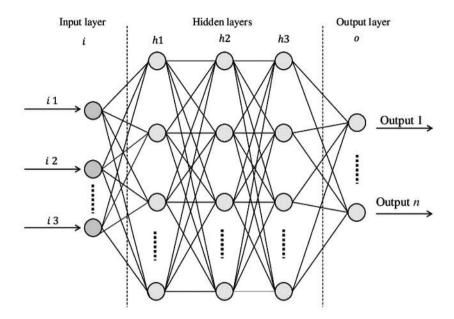

| 4.1   | FNN architecture                                                  | 62  |

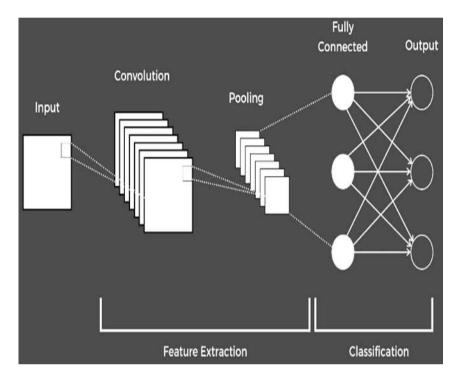

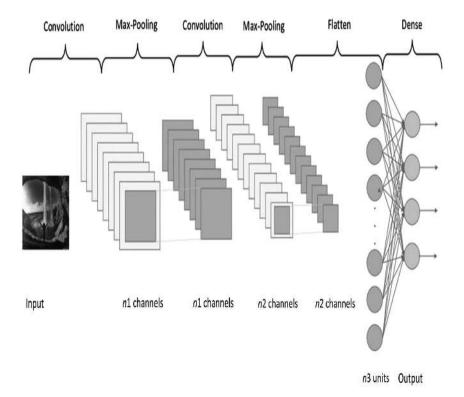

| 4.2   | CNN architecture                                                  | 63  |

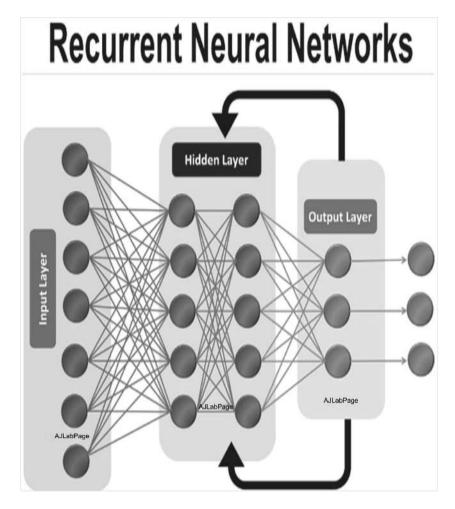

| 4.3   | RNN architecture                                                  | 64  |

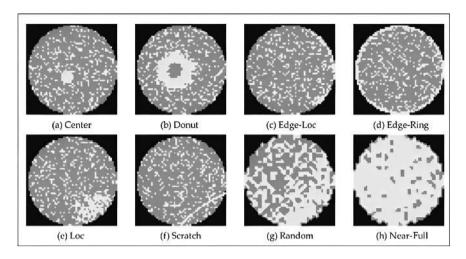

| 5.1   | Defect categorization using semiconductor die images              | 78  |

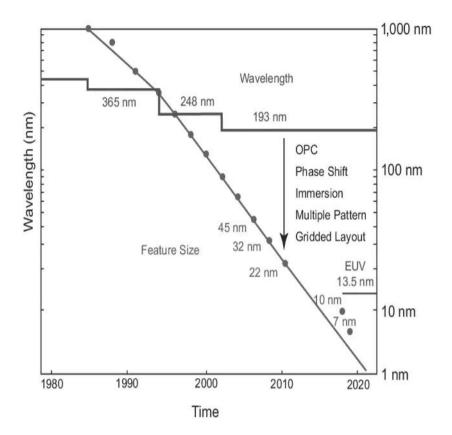

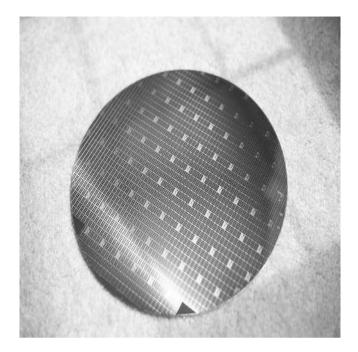

| 5.2   | Showing the defects in semiconductor wafers during production     | 79  |

| 5.3   | Historical progression of IC feature size and photolithography    |     |

|       | technologies                                                      | 80  |

| 5.4   | Convolutional neural network architecture                         | 83  |

| 5.5   | Sample silicon wafer                                              | 86  |

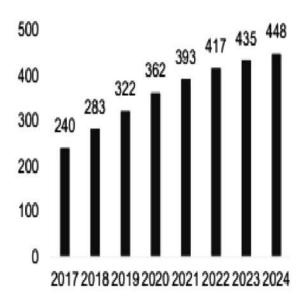

| 6.1   | The global revenues of electronic consumers                       | 104 |

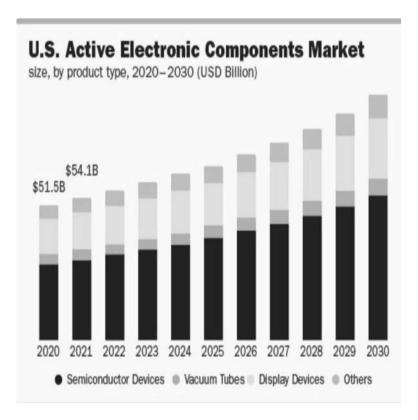

| 6.2   | Demand for semiconductors from 2020 to 2030 in USA                | 105 |

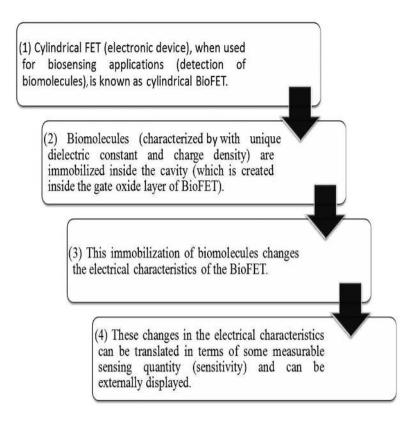

| 7.1   | Fundamental device principle in cylindrical BioFET                | 110 |

| 7.2   | Basic flowchart explaining the implementation of machine learning |     |

|       | in studying BioFET                                                | 112 |

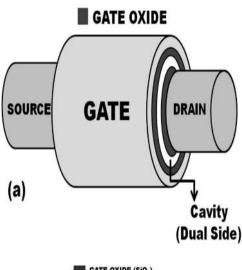

| 1.3             | (a) 3D view, (b) 2D view, and (c) fabrication process flowchart,                                                 | 112        |

|-----------------|------------------------------------------------------------------------------------------------------------------|------------|

| 7.4             | illustrating the basic fabrication steps of a cylindrical BioFET                                                 | 113        |

| 7.4             | Flowchart depicting the summary of methodology used for                                                          | 116        |

| 7 5             | sensitivity analysis                                                                                             | 116        |

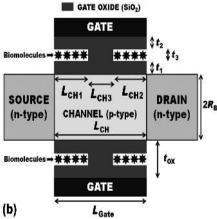

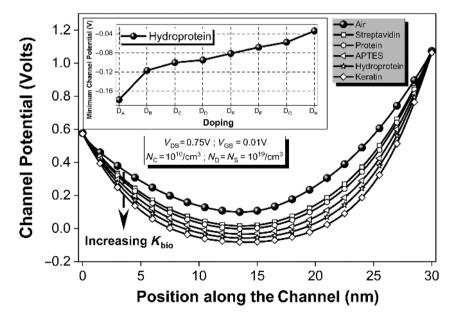

| 7.5             | Visualization of the effect of doping on effective channel length                                                | 118        |

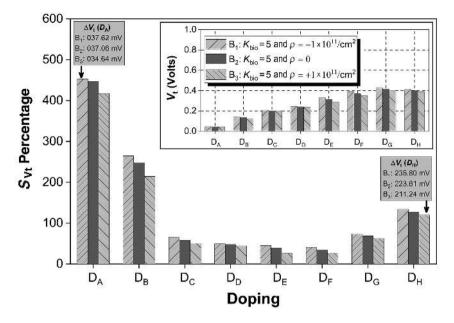

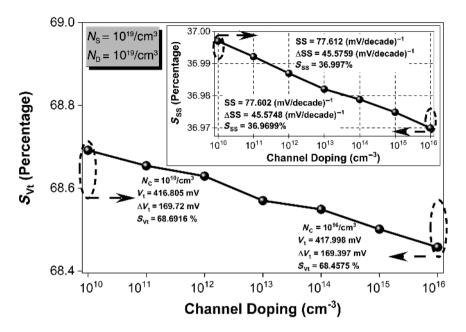

| 7.6             | Threshold voltage sensitivity $(S_{Vt})$ at different doping for different                                       | 110        |

| 7.7             | test biomolecules                                                                                                | 119        |

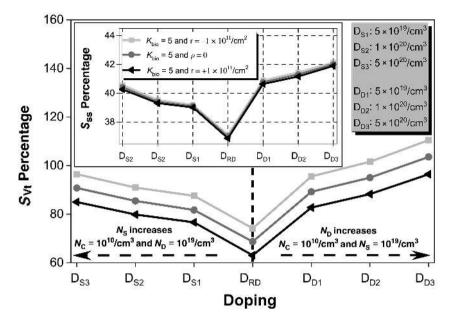

| 7.7             | Threshold voltage sensitivity $(S_{vt})$ at different asymmetric doping                                          | 101        |

| 7.0             | for different test biomolecules                                                                                  | 121        |

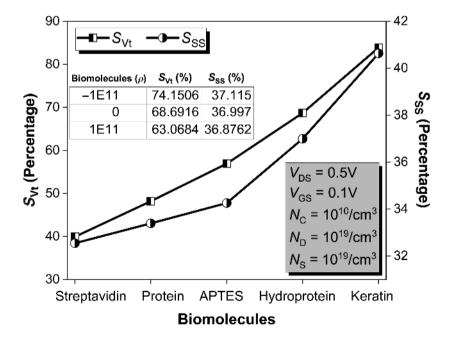

| 7.8             | Threshold voltage sensitivity and subthreshold slope sensitivity in                                              | 100        |

| 7.0             | the presence of different neutral biomolecules                                                                   | 122        |

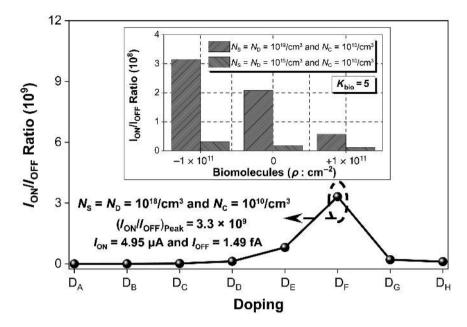

| 7.9             | $I_{\rm ON}/I_{\rm OFF}$ ratio at different doping for hydroprotein                                              | 123        |

| 7.10            | Threshold voltage sensitivity at different channel doping for                                                    | 10.4       |

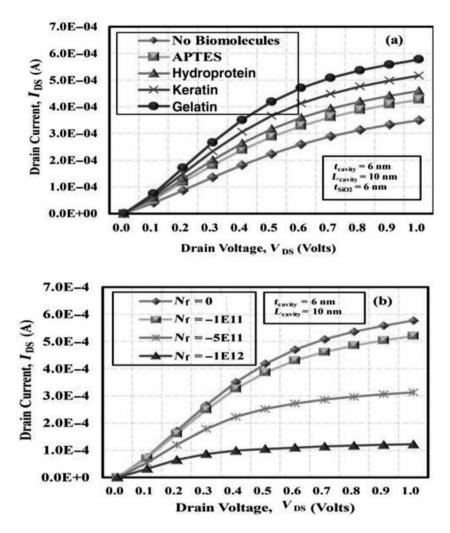

| 7 1 1           | hydroprotein                                                                                                     | 124        |

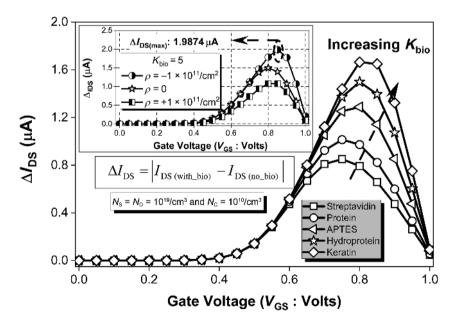

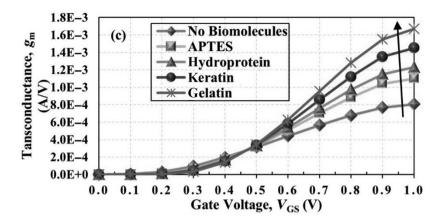

| 7.11            | Change in drain current as a function of gate voltage at $V_{DS} = 0.5 \text{ V}$                                | 104        |

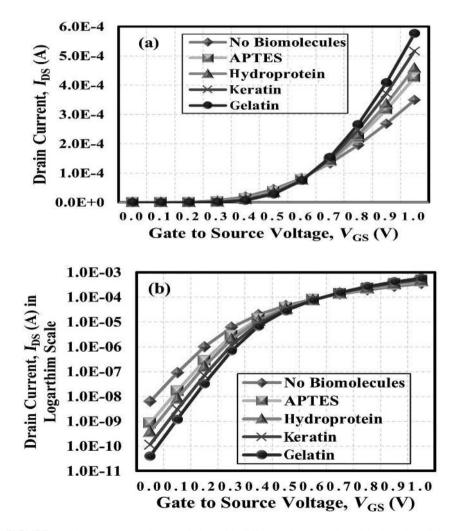

| 7 1 2           | for different neutral biomolecules                                                                               | 124        |

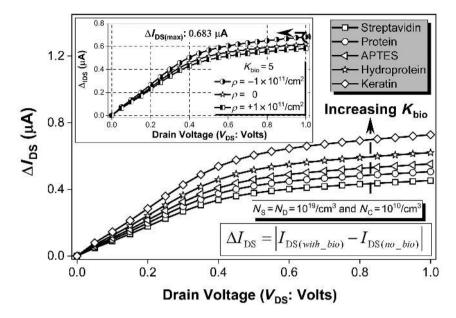

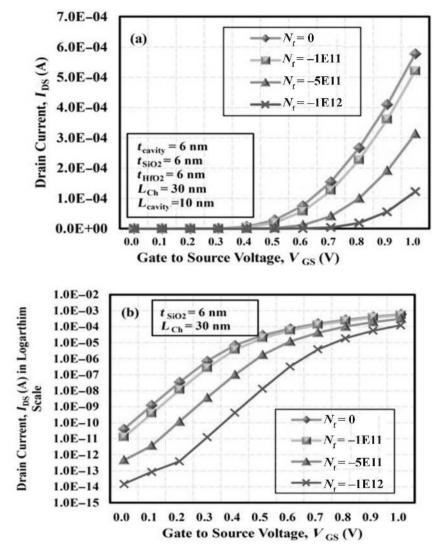

| 7.12            | Change in drain current as a function of drain voltage at $V_{GS} = 0.5 \text{ V}$ for different posters because | 105        |

| 7 1 2           | 0.5 V for different neutral biomolecules                                                                         | 125        |

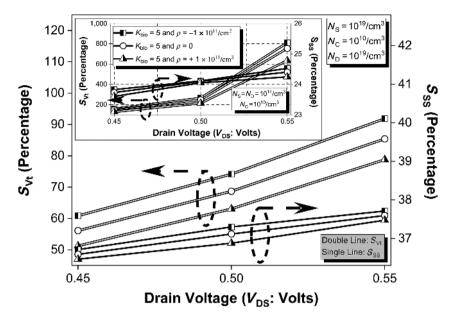

| 7.13            | Threshold voltage sensitivity and subthreshold slope sensitivity at                                              | 100        |

| 714             | various drain voltages for different biomolecules at high doping                                                 | 126        |

| 7.14            | Potential across the channel in the presence of different biomolecules                                           | 126        |

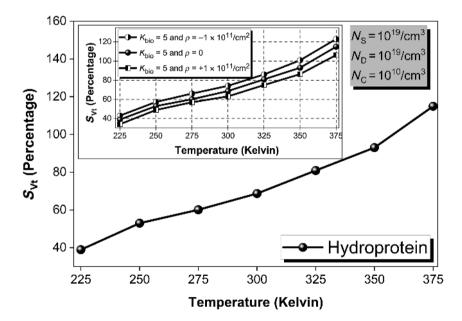

| 7.15            | Threshold voltage sensitivity variation at different temperatures for                                            | 107        |

| 7.16            | hydroprotein The hold of the second is the second in the first form.                                             | 127        |

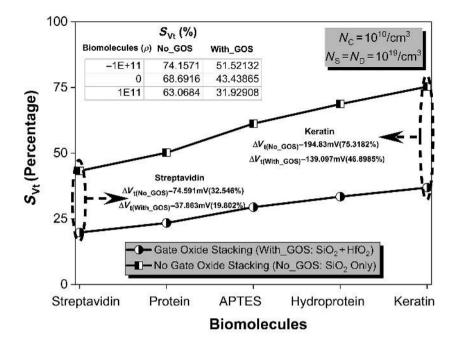

| 7.16            | Threshold voltage sensitivity with and without gate oxide stack for                                              | 120        |

| 7 17            | different neutral biomolecules                                                                                   | 128        |

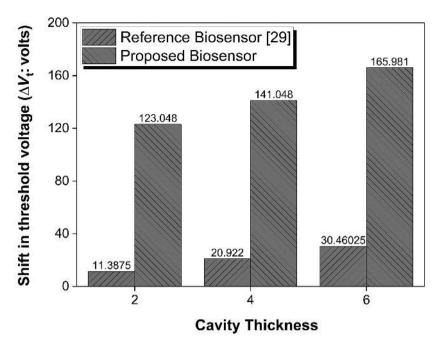

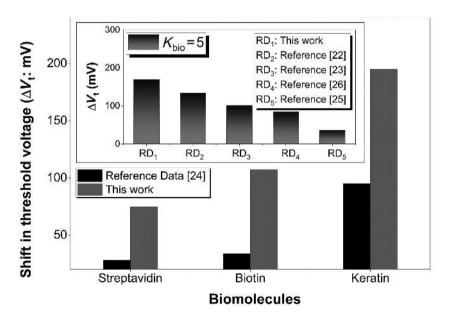

| 7.17            | Comparison chart showing the shift in threshold voltage for APTES                                                | 120        |

| 7 10            | at different cavity thicknesses                                                                                  | 130        |

| 7.18            | Comparison chart showing the shift in threshold voltage for different biomolecules                               | 120        |

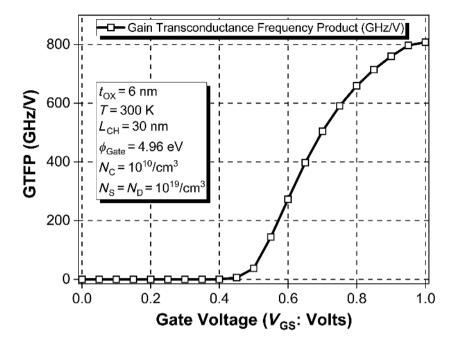

| 7.19            |                                                                                                                  | 130<br>131 |

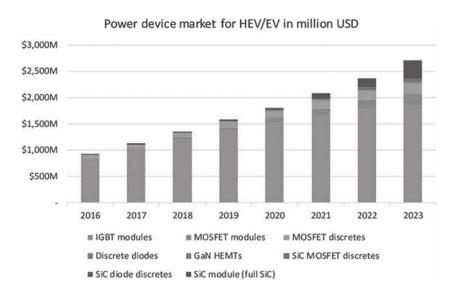

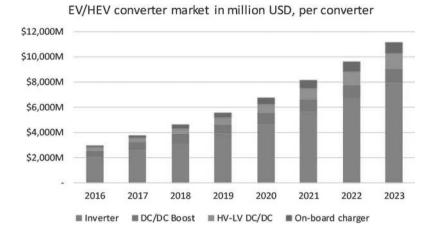

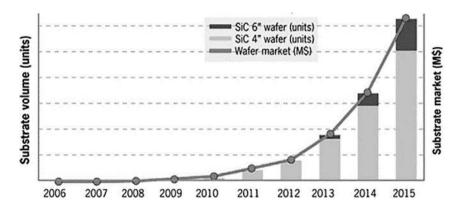

| 7.19<br>3.1     | Gain transconductance frequency product plot Recent advances and trend of HEV/EV-oriented power semiconduc-      | 131        |

| 5.1             | tors: An overview                                                                                                | 143        |

| 3.2             | Recent advances and trend of HEV/EV-convertor market: An overview                                                | 143        |

| 3.2             | Photovoltaic inverters in SiC substrate market in units                                                          | 145        |

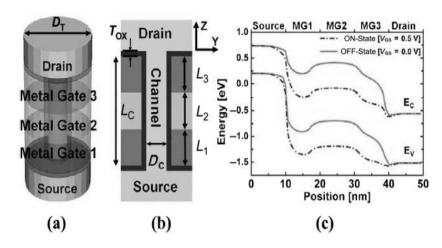

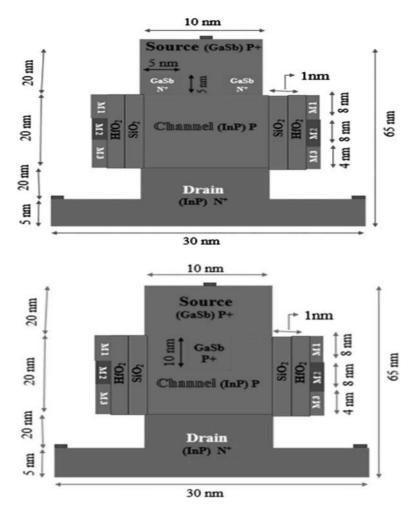

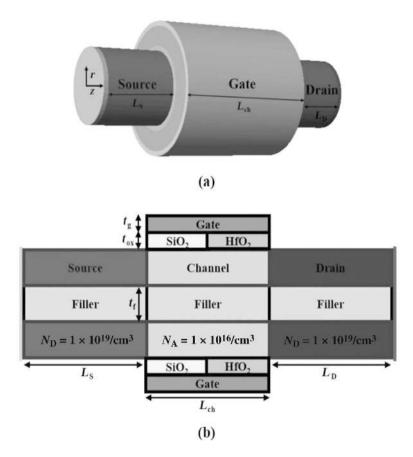

| 9.1             | (a) Depicts the 3D device structure of TMG V-TFET, (b) 2D view,                                                  | 143        |

| 7.1             | and (c) shows the energy band diagram                                                                            | 159        |

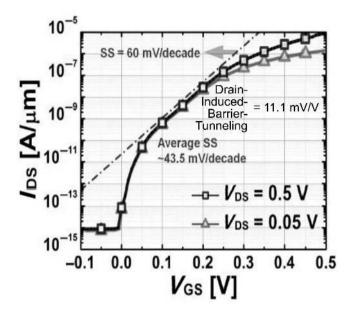

| 9.2             | Transfer characteristics ( $I_{DS}$ – $V_{GS}$ ) of TMG V-TFET                                                   | 160        |

| 9.2<br>9.3      |                                                                                                                  | 100        |

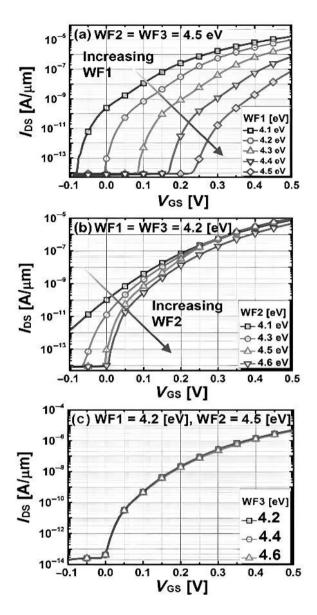

| 9.3             | Transfer characteristics $(I_{\rm DS}-V_{\rm GS})$ of TMG V-TFET for different WF1, WF2, and WF3                 | 161        |

| 9.4             | Device structure of NW-based TMG V-TFET: (a) 3D device                                                           | 101        |

| 7. <del>4</del> | structure and (b) 2D device structure                                                                            | 162        |

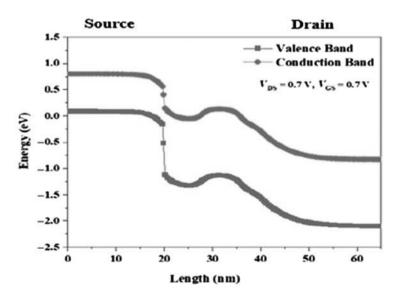

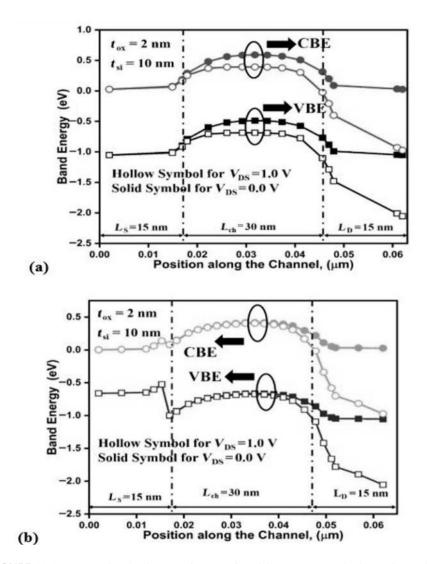

| 9.5             | NW-based TMG V-TFET energy-band diagram                                                                          | 162<br>163 |

| 9.5<br>9.6      | NW-based TMG V-TFET energy-band diagram  NW-based TMG V-TFETs transfer characteristics                           | 164        |

| 9.0<br>9.7      | Schematic of (a) device A-TM-GS-V-TFET with source pocket and                                                    | 104        |

| ).I             | (b) device B-TM-GS-V-TFET with source extension                                                                  | 165        |

|                 | TOT GOVICE DELIVITORE VELLEN WITH SOUTH CARCITATION                                                              | 103        |

| List of Figu | ires and | <b>Tables</b> |

|--------------|----------|---------------|

|--------------|----------|---------------|

|   |   | • | • |

|---|---|---|---|

| Y | V | ı | ı |

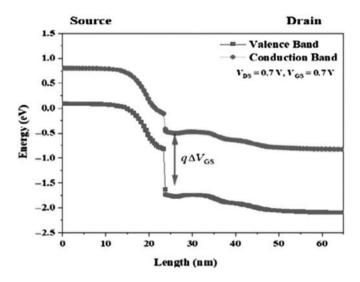

| 9.8    | Energy-band diagram: (a) TM-GS-V-TFET with source pocket                                         |     |

|--------|--------------------------------------------------------------------------------------------------|-----|

|        | (Device A) and (b) TM-GS-V-TFET with source extension (Device B)                                 | 166 |

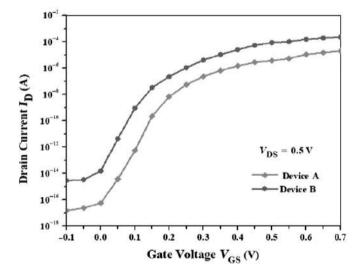

| 9.9    | Transfer characteristics of TM-GS-V-TFET with source pocket                                      |     |

|        | (Device A) and with source extension (Device B)                                                  | 167 |

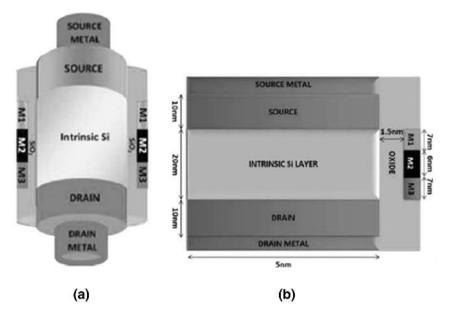

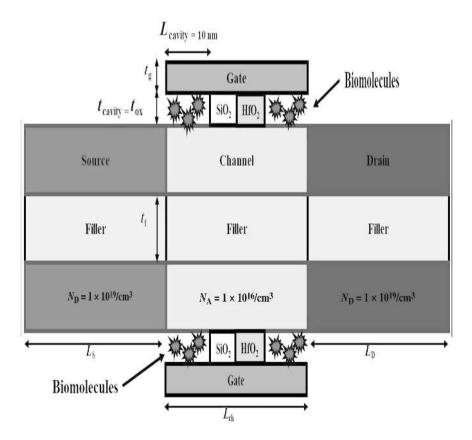

| 10.1   | (a) 3D representation of MC-DD-Ge/Si-INW-FET and (b) 2D                                          |     |

|        | representation of MC-DD-Ge/Si-INW-FET                                                            | 175 |

| 10.2   | Energy-band diagram for (a) for CGAA FET and (b) MC-DD-Ge/                                       |     |

|        | Si-INW-FET                                                                                       | 178 |

| 10.3   | Off-state leakage along channel for various devices                                              | 179 |

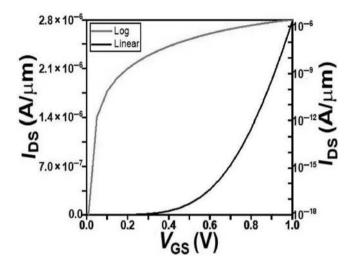

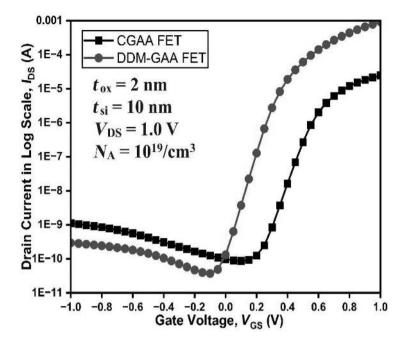

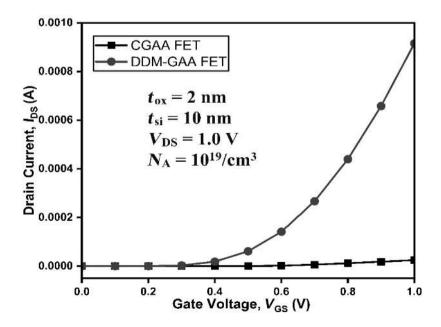

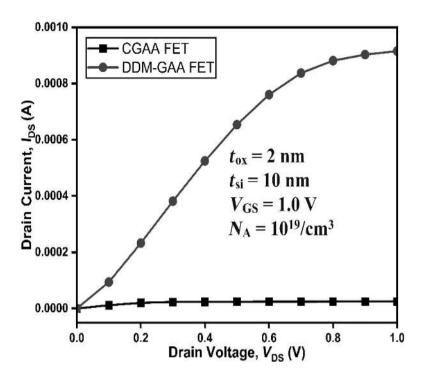

| 10.4   | The variation of drain current with respect to gate voltage                                      | 179 |

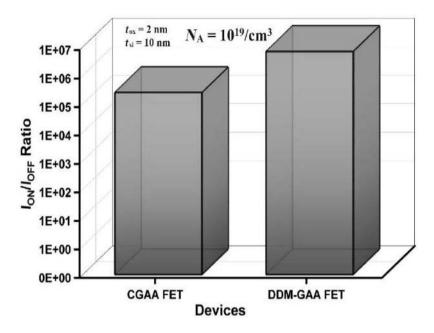

| 10.5   | The variation of $I_{ON}/I_{OFF}$ in various devices                                             | 180 |

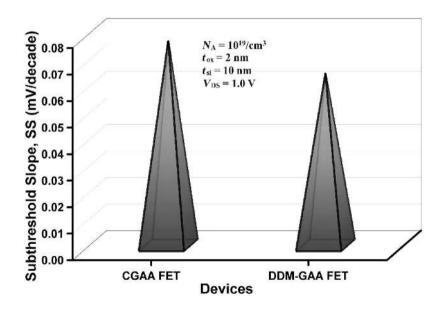

| 10.6   | The variation of subthreshold slope in various devices                                           | 180 |

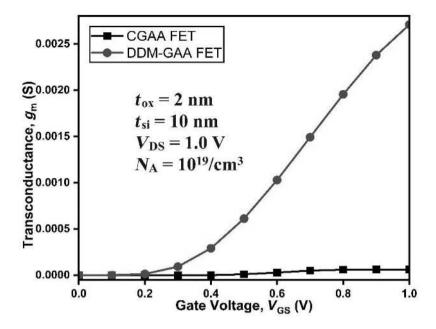

| 10.7   | The variation of transconductance in various devices                                             | 181 |

| 10.8   | The variation of subthreshold slope in various devices                                           | 182 |

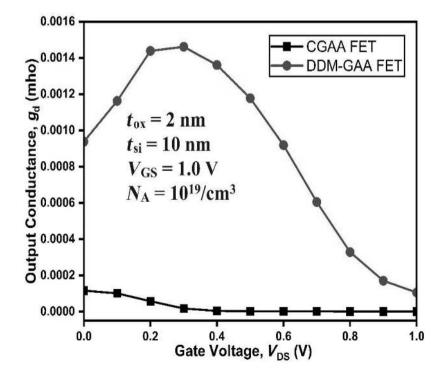

| 10.9   | The variation of output conductance in various devices                                           | 182 |

| 10.10  | Two-dimensional structure of MC-DD-Ge/Si-INW-FET as                                              |     |

|        | a biosensor                                                                                      | 185 |

| 10.11  | Surface potential along the channel of MC-DD-Ge/Si-INW-                                          |     |

|        | FET biosensor for (a) various neutral biomolecules and (b) DNA                                   |     |

|        | biomolecules at $K = 12$ and varying charges                                                     | 186 |

| 10.12  | Electric field of MC-DD-Ge/Si-INW-FET biosensor for (a) vari-                                    |     |

|        | ous neutral biomolecules and (b) DNA biomolecules at $K = 12$ and                                |     |

|        | varying charges                                                                                  | 187 |

| 10.13  | (a) $I_{\rm D}$ - $V_{\rm GS}$ characteristics with different biomolecules with changing         |     |

|        | dielectric constant, (b) drain current in logarithmic scale represent-                           |     |

|        | ing the subthreshold current at $V_{GS} = 0.0$ V, and (c) transconduc-                           |     |

|        | tance for different biomolecules                                                                 | 188 |

| 10.14  | (a) $I_D$ – $V_{GS}$ characteristics of MC-DD-Ge/Si-INW-FET biosensor                            |     |

|        | for charged DNA biomolecules and (b) drain current in logarithmic                                |     |

|        | scale for charged DNA biomolecules                                                               | 190 |

| 10.15  | $I_{\rm D}$ - $V_{\rm DS}$ characteristics of MC-DD-Ge/Si-INW-FET biosensor for                  |     |

|        | (a) neutral biomolecules and (b) charged DNA biomolecules                                        | 191 |

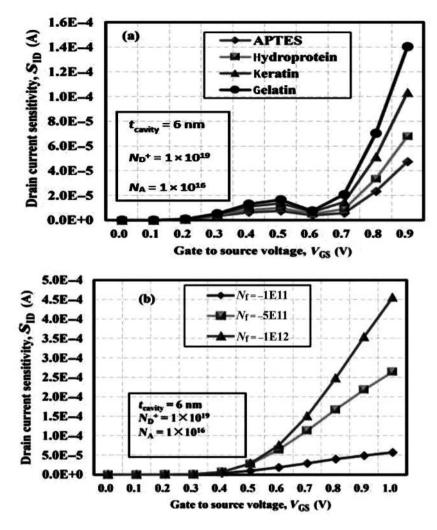

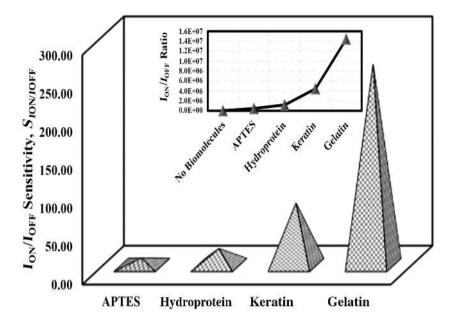

| 10.16  | Drain current sensitivity for (a) different biomolecules and (b) DNA                             |     |

|        | biomolecules with increased negative charge                                                      | 192 |

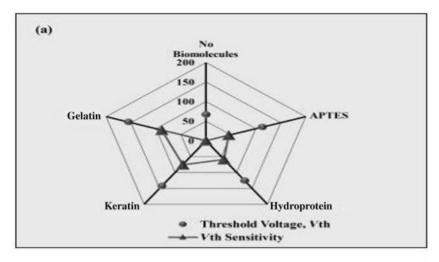

| 10.17  | Threshold voltage and threshold voltage sensitivity for various (a)                              |     |

|        | neutral biomolecules and (b) charged DNA biomolecules                                            | 193 |

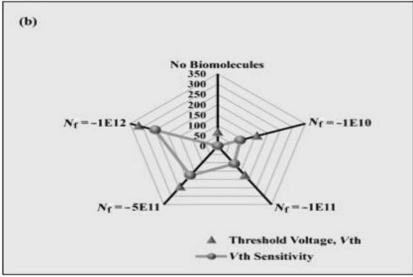

| 10.18  | $I_{\rm ON}/I_{\rm OFF}$ ratio and $I_{\rm ON}/I_{\rm OFF}$ sensitivity of DDM-GAA FET biosensor | 195 |

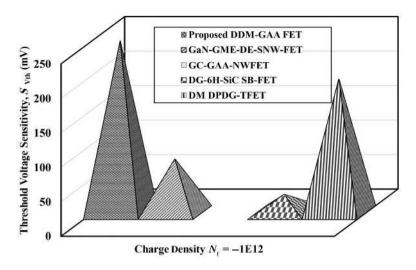

| 10.19  | VIII -                                                                                           |     |

|        | recently published FET biosensors                                                                | 196 |

| Tables |                                                                                                  |     |

| 2.1    | Original Dimensions                                                                              | 26  |

| 2.2    | Modified Dimensions                                                                              | 26  |

| 7.1    | Structural Parameters                                                                            | 115 |

| 7.2    | Shift in Threshold Voltage for Different Biomolecules                                            | 117 |

| 7.3    | SS and $S_{SS}$ Variation at Different Symmetric Doping                                          | 120 |

| 7.4    | $V_{\rm t}$ and SS Variation at Different Asymmetric Doping                                      | 122 |

| 7.5  | Effect of Fill-In Factor and Location of Different Biomolecules   |     |

|------|-------------------------------------------------------------------|-----|

|      | on $S_{ m v_t}$                                                   | 129 |

| 9.1  | Important Design Specifications of GAA-Based TMG V-TFET           | 159 |

| 9.2  | Important Design Parameters of NW-Based TMG V-TFET                | 162 |

| 9.3  | Device Specifications of TM-GS-V-TFET                             | 166 |

| 9.4  | Comparison Data of the DC Characteristics of Different TMG V-TFET | 168 |

| 10.1 | Parameter Specifications                                          | 176 |

| 10.2 | Simulation Employed Models                                        | 177 |

# 1 Semiconductor Materials Current Applications and Limitations of Advanced Semiconductor Devices

C. Shekhar

#### 1.1 INTRODUCTION

Semiconducting materials have played a significant role in the information revolution. The main characteristic of semiconducting materials is the resistivity values falling between those of metals and insulators and that can be tuned with different approaches of material fabrication. The tunable electrical resistivity of these materials has enabled the development of a wide variety of electronic devices that have fundamentally changed the way humans interact among themselves or share, store, and create knowledge and data and changed the world as well. The developments of semiconductor materials started in the 19th century with the discovery of electrical conductivity by Alessandro Volta. Alessandro Volta devised the Voltaic pile, known as the first electrical battery, leading to the development of the study of electrical properties of different types of materials.1 Following this, in 1833, Michael Faraday studied the corelations between the amount of electricity passing through a solution and the amount of chemical change in the solution and presented the laws of electrolysis, thereby establishing the electron as the carrier of the electrical charge in electrical solutions.<sup>2</sup> Another notable discovery was made in 1873 by Frederick Guthrie, who found the phenomenon of thermionic emission, in which a hot metal rod exerts a force of attraction or repulsion on lightweight objects. Thermionic emission later became the basis of vacuum tubes used to modulate signals for amplification or rectification.<sup>3</sup> The advent of vacuum tubes led to development of electronic devices and the electronic industry. However, due to the inherent disadvantages of vacuum tubes, such as being large, bulky structures, and unreliable output, the demand for more efficient and compact electronic devices kept the search ongoing.4

In 1904, John Ambrose Fleming invented the diode, a two-terminal electronic device that allows current to flow in only one direction. The diode was made from a vacuum tube with a heated cathode and cold anode.<sup>5</sup> In 1906, Lee De Forest invented the triode, a three-terminal electronic device that could be used to amplify electrical signals. The triode was made from a vacuum tube with a heated cathode, cold anode, and control grid. Vacuum tubes were used in a variety of applications, including

DOI: 10.1201/9781003508304-1

1

radio, television, and radar. However, they were still large, bulky, and unreliable. This led to a search for a more efficient and compact electronic device.<sup>6</sup>

The continued effort and search to replace vacuum tubes with more efficient, compact, and reliable electronic devices led J. Bardeen, W. Brattain, and W. Shockley in 1947 to develop transistors. The transistor is a semiconductor device capable of amplifying and switching electrical signals made by arranging extrinsic semiconductors in PNP or NPN format. Due to its improved properties, the transistor replaced vacuum tubes in different applications and fuelled the proliferation of a variety of electronic devices. This further led to the invention of the integrated chip (IC) by J. Kilby and R. Noyce in 1950, which is a compact electronic device housing thousands of transistors and other electronic structures. Uth the development of ICs, it became possible to design and fabricate highly complex electronic structures at a reduced cost, leading to the development of power-efficient, compact electronic devices with greater computing power, thus giving rise to the modern electronic revolution. Such electronic devices are used in everything from computers to watches, missiles, aircraft, and smartphones.

#### 1.2 TRADITIONAL SEMICONDUCTORS

#### 1.2.1 SILICON (SI)

Silicon (Si) is among the most abundant materials in the earth's crust, making up almost 27% of it. Additionally, it has favourable electronic properties, which can be tuned by different approaches. Its semiconducting nature is most useful for the electronic industry; therefore, it has been most widely used for the manufacturing of electronic components for the electronic industry. The properties of silicon have paved the way for it being used to fabricate many electronic components for use in a multiplicity of applications; therefore, silicon has dominated the semiconductor industry for many years. Among the many components fabricated on a large scale from silicon are transistors, diodes, ICs, sensors, and solar cells, to mention a few. This section highlights the significance of silicon as the material of choice for the semiconductor industry along with some of its prominent limitations for advanced applications.<sup>12</sup>

After oxygen, silicon is the most abundant material present on the earth. It is generally extracted from silica sand. Its abundance and availability make it a suitable candidate for large-scale use. High-quality silicon crystals are grown from the solution obtained from silicon dioxide, which is needed for the fabrication process in the semiconductor industry. With the low bandgap of 1.12 eV, silicon allows the effective control of charge carriers at room temperature, and with suitable doping, the carrier concentrations can be controlled by adding aliovalent cations to the Si lattice. This ability to effectively control carrier concentrations, and therefore the conductivity of Si, makes it a suitable candidate for applications such as transistors, switching devices, and amplifiers. When silicon is exposed to oxygen, it forms an insulating layer of SiO<sub>2</sub> readily, which is critical for the fabrication of metal oxide semiconductor field effect transistors (MOSFETs). MOSFETs have been central to many electronic components in digital and analog circuits. Additionally, SiO<sub>2</sub>, formed on

exposure of silicon to oxygen, provides much-needed electrical insulation between different components when desired, enhancing the reliability of the electronic components for prolonged usage.<sup>13</sup>

Since its first development a long time ago, Si-based industries have created large-scale synthesis and fabrication capabilities – particularly, the Si-based ICs and complementary metal oxide semiconductor technology, enabling the creation of millions of transistors on a single chip for high-performance computing. The mature infrastructure capabilities, skilled workforce, and cost considerations are some of the reasons for Si being the dominant material over the years in the semiconductor industry.

#### 1.2.2 Limitations of Silicon for Advanced Semiconductor Devices

Though silicon possesses many admirable properties, it has significant limitations, especially in the areas of high-frequency, high-speed devices. Let us look at some of the limitations briefly here: (1) Compared to gallium arsenide (GaAs), the mobility of the charge carrier in silicon is low. For applications requiring high-frequency operations, such as radio-frequency (RF) and microwave devices, materials with a large charge carrier mobility are more efficient. Therefore, materials such as GaAs are preferred over Si for high-speed operation at lower power consumption. (2) Silicon is not the preferred material in areas of power electronics due to its lower thermal conductivity compared to other materials, such as silicon carbide (SiC) or diamond. In high-power applications, the ability to manage the heat generated becomes crucial for its efficient dissipation. Materials such as SiC and diamond are among the preferred materials in power electronics due to better thermal conductivity and higher breakdown voltage. (3) With the advancement of science, particularly in the area of nanotechnology, Si faces challenges at the nanoscale, pertaining to quantum tunnelling and short-channel effects. These effects lead to power leakage and reduced performance for ultra-small transistors.<sup>14</sup> Due to these limitations, the scientific community is looking for other 2D materials, such as graphene, transition metal dichalcogenides, and III-V semiconducting compounds, for next-generation devices.

#### 1.2.3 FUTURE PROSPECTS AND ALTERNATIVES

There is now a class of different semiconducting materials suitable for replacing silicon, such as SiC and gallium nitride (GaN). Though Si remains the preferred material of choice in many areas, there is a gradual shift in advanced areas, such as high-power and high-frequency applications. Due to the existing infrastructure, its cost-effectiveness, and wide range of applicability, Si is still greatly favoured.

#### 1.3 TRADITIONAL SEMICONDUCTORS: GERMANIUM (GE)

Another material earlier used for the fabrication of electronic devices is germanium (Ge). It was first used for the preparation of transistors in the early 1940s and 1950s. Transistors made of Ge were widely used before being replaced by Si. Although Ge has been replaced by Si in a majority of areas, it is still the preferred choice

in high-frequency and optoelectronic applications due to its superior charge carrier mobility and direct bandgap, respectively.

With a lower bandgap of 0.66eV, Ge can conduct at close to room temperature as compared to Si, which can only conduct at higher temperatures due to a wider bandgap. This makes it a more suitable candidate for many electronic devices such as diodes and transistors. At the same time, this also means that electronic devices made of Ge are more sensitive to temperature variations, leading to higher leakage currents compared to Si. 13,15 In comparison to silicon, the charge carrier mobility of germanium is significantly higher. The electron and hole mobilities in germanium and silicon are 3,900 cm²/V·s and 1,900 cm²/V·s and ~1500 cm²/V·s and ~450 cm²/V·s, respectively. The higher charge carrier mobility suggests the suitability of germanium in high-frequency applications, in which rapid switching and signal processing are key requirements. Though the charge carrier mobility is significantly higher (149 W/mK) for germanium, its thermal conductivity is lower (60 W/mK). Thus, germanium faces issues in managing the heat generated in power electronics and high-temperature applications.

Before the widespread use of germanium, vacuum tubes were used for the amplification of signals. The use of Ge revolutionized the process and led to the fabrication of the first bipolar junction transistors in the 1940s. This development enabled the creation of compact and energy-efficient amplifiers, replacing the vacuum tubes. Till the 1960s, Ge was dominant; it was used to make a wide variety of electronic devices from radio to the early computers. But the sensitivity of Ge for higher temperatures and its relatively higher cost compared to Si eventually led to silicon replacing it. The ability of silicon to form  $\mathrm{SiO}_2$  with oxygen led to the development of MOSFETs, which laid the foundations of the modern electronic industry.  $^{16}$

#### 1.3.1 CURRENT APPLICATIONS AND LIMITATIONS

Although Ge was replaced by Si in many applications, its use in many applications is still mainstream, as described here:

- High-Speed Transistors: The higher carrier mobility of Ge is suitable for high-frequency and high-speed transistors, considering the switching frequency and power consumption requirements.

- **Optoelectronics:** The lower bandgap of Ge is suitable for the detection and measurement of low-energy radiations, such as infrared (IR) and fibre optic communication systems.

- **Solar Cells:** Ge can enhance the energy efficiency of the substrate in multijunction solar cells and also has space applications.

- Alloys and compounds: Ge is very often alloyed with Si; for example, SiGe alloy is used in RF and microwave applications.

Regardless of these advantages, Ge has limitations, such as being expensive to process, lower thermal conductivity, and inability to form an oxide layer like  $\mathrm{SiO}_2$ , all of which limit its applications and render it less versatile in MOSFET applications.

#### 1.3.2 FUTURE PROSPECTS

With the growing demand for compact, faster, and more energy-efficient devices, there is renewed interest in Ge-based electronic devices to overcome the scaling limitations of Si. Moreover, there are efforts to investigate Ge's use in quantum computing and photonic devices, where its unique electrical and optical properties may offer additional advantages. There are therefore possibilities for the use of Ge in new and specialized ways in electronic devices.

#### 1.4 GALLIUM ARSENIDE (GAAs)

GaAs is a direct bandgap, III-V semiconductor. It has been used in critical applications, such as microwave and millimetre-wave devices, photovoltaic cells, and light-emitting diodes (LEDs). Being a direct bandgap semiconductor and a key material in the electronics industry for a long time, it offers unique advantages over traditional materials, such as Si, particularly in high-frequency, high-speed, and optoelectronic applications.

The bandgap of GaAs is 1.42 eV at room temperature, whereas Si is an indirect bandgap material. This makes GaAs more energy efficient for electron transitions from the conduction band to the valence band and vice versa, leading to effective photon emission. Thus, GaAs is widely used in optoelectronic applications such as laser diodes and LEDs.

The charge carrier mobility of GaAs is ~8,500 cm²/V·s, which is significantly higher compared to Si (1,500 cm²/V·s). The higher carrier mobility translates to a quick response to the applied external field, making GaAs more suitable for high-frequency, high-speed applications, such as microwave transistors and field effect transistors (FETs). GaAs-based devices can be effectively used in the GHz frequency range, which is suitable for RF and microwave communication systems. The higher stability of GaAs-based devices against radiation damage also places these devices ahead of Si-based devices for space and satellite applications, where the performance of the latter can degrade significantly. GaAs-based devices show higher performance stability for longer periods in harsh conditions.<sup>17</sup>

#### 1.4.1 APPLICATIONS OF GAAS IN SEMICONDUCTOR DEVICES

Due to the low direct bandgap, high carrier mobility, and high saturation velocity, GaAs-based devices have been extensively used in high-frequency and optoelectronic applications. GaAs-based devices – for example, microwave and millimetre-wave transistors such as heterojunction bipolar transistors and high-electron-mobility transistors – have been widely used for many applications, like telecommunications, radar, wireless communication systems, optoelectronics, solar cells, LEDs, and laser diodes. Photovoltaic systems such as GaAs-based solar cells have been used in satellite and space applications due to their high efficiency, durability, and high performance under extreme radiation exposure for long periods of time. Also, GaAs is the preferred material for the fabrication of monolithic microwave integrated Circuits (MMICs), integral for radar, satellite, and cellular-based communication systems.

Additionally, due to its direct bandgap, GaAs is ideal for optoelectronic applications such as efficient LEDs and laser devices.<sup>18</sup>

#### 1.4.2 LIMITATIONS OF GALLIUM ARSENIDE

Although there are many advantages of GaAs, its drawbacks have limited its application in many areas. GaAs is expensive to synthesize compared to Si primarily due to the scarcity of Ga. The wafer fabrication of GaAs is complex, increasing the overall cost and limiting its use to specialized high-performance applications. Its mechanically fragile nature makes it difficult to handle during the fabrication process, thus making it challenging to scale the production of GaAs-based systems. Its lower thermal conductivity limits its application where heat dissipation is critical for device performance. Due to these issues, SiC and GaN are preferred instead in many applications.

#### 1.4.3 FUTURE PROSPECTS

Although GaAs is critical for many applications, materials like SiC and GaN are also used for power electronics and high-performance transistors. GaAs continues to be critical for high-frequency and optoelectronic applications where efficient light emission and stability against solar radiation are critical requirements.

#### 1.5 ADVANCED SEMICONDUCTOR MATERIALS

With the advancement of science and technology and electronic devices, in particular, the demand for compact, energy-efficient devices have increased in recent years. The properties of traditional semiconducting materials limit their applications in many areas, such as power electronics, telecommunications, and optoelectronics. These limitations have led to the development of newer materials with superior physical and chemical properties for such applications. Among other materials, silicon carbide (SiC), gallium nitride (GaN), and indium phosphide (InP) are useful and promising candidates for engineering and technological applications.

#### 1.6 SILICON CARBIDE (SIC)

#### 1.6.1 Properties and Advantages

Silicon carbide – the wide-band semiconductor with a bandgap of 3.26 eV, high breakdown voltage, high thermal conductivity, mechanically hard, and thermal and structural stability at high temperatures and frequencies – is a suitable candidate for devices that operate at high frequencies and high voltages in the area of power electronics. Its high thermal conductivity (~4.9 W/cm·K) ensures efficient thermal management in high-temperature applications without the need for detailed cooling supports for the device, making such devices rugged enough to function under harsh conditions. The devices made of SiC, such as MOSFETs and Schottky diodes, show much lower ON-state resistance and switching losses as compared to traditional semiconductor-based devices, leading to drastically improved efficiencies. These

characteristics are critical for many energy-sensitive applications, such as electric vehicles (EVs), renewable energy systems, and industrial motor drives.<sup>19</sup>

#### 1.6.2 CHALLENGES AND CURRENT DEVELOPMENTS

Though there are significant advantages with the properties of SiC for applications in critical areas, there are limitations too: (1) The cost and complexity of SiC-based devices is way higher than that for the Si-based devices. (2) SiC is a superhard and brittle material and requires special care to polish and cut the crystal into fibres for the fabrication processes. Thus, the wafer manufacturing is a costly and complex process. The technology for the fabrication of SiC wafers is not yet as mature as for Si-based devices.

To address these challenges and harness the unique properties of SiC, there have been sustained efforts to develop technologies to circumvent its limitations. Some of the efforts centred on developing physical vapour deposition (PVD), chemical vapour deposition (CVD), and single crystal growth processes to improve the availability of SiC crystals and wafers. These improvements have led to the enhanced usage of the material for commercial applications. Additionally, efforts for a new electronic architecture development and fabrication process are in focus. This has resulted in trench MOSFET structures, created to minimize ON-state resistance and improve the performance of SiC-based devices.

#### 1.6.3 APPLICATIONS

The primary application of SiC is in power electronics, where it is used in high-voltage, high-temperature, and high-efficiency devices. SiC MOSFETs and Schottky diodes are increasingly being used in power converters, inverters, and motor drives due to their ability to operate at higher switching frequencies and temperatures compared to silicon-based devices. This enables more compact, efficient, and reliable power systems, especially in EVs, industrial equipment, and renewable energy installations.

In the automotive industry, SiC is being used in the powertrains of electric and hybrid vehicles to improve efficiency and reduce the size and weight of power electronics systems. The high thermal conductivity of SiC allows for more effective heat dissipation, reducing the need for large cooling systems and enabling more compact designs.

SiC is also finding applications in aerospace and defence, where its ability to withstand extreme temperatures and radiation makes it suitable for use in harsh environments. SiC devices are also used in satellite communication systems, radar, and high-temperature sensors.

#### 1.7 GALLIUM NITRIDE (GAN)

#### 1.7.1 Properties and Advantages

With a bandgap of 3.4 eV, gallium nitride is a preferred choice for many applications. The bandgap of GaN is even greater than that of SiC; it has high carrier mobility and

saturation velocity, enabling its use in high-frequency applications, and GaN-based devices work at speeds much greater than that for Si-based devices. Due to these properties, GaN can be used for a multiplicity of applications involving high frequency and high power, such as RF, power transistor, and high-speed communication systems.

Gallium nitride has a high breakdown voltage and thermal stability. It is stable at high voltages and elevated temperatures. Due to its high thermal conductivity, it can efficiently operate at higher temperatures without the need for cooling systems. In addition, GaN crystals have high charge carrier mobility. Also, due to the compatible lattice parameters, GaN can be grown on silicon. It therefore can utilize the existing fabrication and manufacturing techniques for silicon, enabling the integration of technology tailored for Si to be used for GaN.<sup>20</sup>

#### 1.7.2 CHALLENGES AND CURRENT DEVELOPMENTS

There are many challenges to the development of GaN as the mainstream electronic material as compared to Si primarily due to the complexity of the manufacturing process involved. The cost of the manufacturing process is larger as compared to that of Si, thus limiting GaN's applicability. There are reliability issues in high-power applications, and GaN-based devices are prone to degradation in high-stress conditions.

Among the current developments in GaN-based applications, they have shown improved performance in the area of high switching speeds with low losses. The emphasis is on the development of compact electronic devices with better design and packaging techniques and improved efficiencies. Recent developments have focused on their applications in electric mobility, improving the power efficiency of charging stations, and enhancing the range of electrical vehicles.

#### 1.7.3 APPLICATIONS

GaN is widely used in high-frequency and high-power applications, such as RF amplifiers, power transistors, and microwave devices. Its high electron mobility and saturation velocity make it ideal for use in high-frequency communication systems, including 5G networks and satellite communication.<sup>21</sup>

In the power electronics sector, GaN devices are being used in power converters, inverters, and motor drives, where their high efficiency and fast switching speeds lead to significant energy savings. GaN is also being used in power supplies for data centres and telecommunications equipment, where its ability to handle high voltages and operate at high frequencies helps to reduce power consumption and heat generation.<sup>22</sup> GaN is also finding applications in optoelectronics, particularly in LEDs and laser diodes. GaN-based LEDs are widely used in solid-state lighting, display technology, and automotive lighting due to their high efficiency and brightness.

## 1.8 ADVANCED SEMICONDUCTOR MATERIALS: 2D MATERIALS – GRAPHENE AND TRANSITION METAL DICHALCOGENIDES

There have been tremendous advances in information technology based on the availability of better products that are used for the storage, transfer, and processing of information in enormous quantities. This has been possible primarily due to the

availability of semiconductors capable of operating at these scales. The present density of transistors, their energy efficiency, operating temperatures, thermal management capacities, and operational frequencies are at previously unimaginable levels. Due to the ever-increasing demand for better products, there is a requirement for materials with improved properties that can extend the limits of present-day electronic devices. In the recent past, there has been significant development in the areas of 2D materials such as graphene and transition metal dichalcogenides (TMDs), which can be promising candidates due to their excellent physical and chemical properties that are crucial for their use in electronic devices.

The much-famed 2D materials consist of a two-dimensional extended layer of atoms with the thickness of a few atomic layers. This leads to a dramatic alteration of the properties of this material due to the quantum confinement effects in the 2D materials. Among 2D materials, graphene is the most important material reported in 2004, which is a single-layer thick carbon sheet arranged hexagonally. In addition, TMDs such as molybdenum disulfide (MoS<sub>2</sub>) and tungsten disulfide (WS<sub>2</sub>) have attracted great attention because of their superior semiconducting properties.

#### 1.9 GRAPHENE: THE PIONEER OF 2D MATERIALS

#### 1.9.1 DISCOVERY AND STRUCTURE

Graphene was prepared by A. Gein and K. Novoselov in 2004, and they won the 2010 Nobel Prize in Physics for the discovery of this remarkable material. It consists of a hexagonal arrangement of carbon atoms in a single layer, creating an electronic band structure that results in unique physical and chemical properties. Graphene has zero bandgap – that is, it's a semimetal. The topmost of the valance band and lowest of the conduction band touches at the Dirac point, resulting in the massless Dirac fermions, thus imparting excellent physical and chemical properties to graphene.<sup>23</sup>

#### 1.9.2 Properties

The single-layer carbon, arranged in a hexagonal pattern forming the zero bandgap material, has excellent physical properties, which are extremely useful in electronic device applications. Graphene exhibits enormous electron mobility of 2 × 10<sup>5</sup> cm<sup>2</sup>/Vs under ideal conditions.<sup>24</sup> Such a value of electron mobility is remarkably high compared to traditional conductors such as silver and copper. Graphene is extremely strong, with 130 GPa tensile strength, almost 200 times that of steel.<sup>24</sup> Its thermal conductivity is of the order of 5,000 W/mK, making it the ideal candidate for thermal management in electronic devices.<sup>25</sup> It only absorbs a very small portion of the electromagnetic radiation incident on it. Graphene is a highly transparent material and suitable for optoelectronic applications.<sup>26</sup> Although is very strong compared to steel, graphene is flexible at the same time and can be stretched by almost 20%, making it the best candidate for flexible electronics.

#### 1.9.3 APPLICATIONS

The high mobility of graphene has made it a most suitable candidate for replacing traditional electronic materials to make FETs, and devices made of graphene can be used at high signal frequencies, leading to devices with much faster speeds. The

large surface area and high electrical conductivity of graphene make it suitable for use in high-storage batteries and supercapacitors, significantly increasing the energy density of these devices.<sup>27</sup> It is also useful for surface-sensitive applications such as sensors for gas detection, chemicals, and other molecules.<sup>28</sup> The flexible nature of graphene makes it a much desired candidate for flexible electronics, wearables, and foldable displays, to mention a few applications.<sup>29</sup> In addition to this, the transparent nature of graphene has many applications in optoelectronic devices, such as LEDs transparent electrodes, and photodiodes.<sup>30</sup>

#### 1.9.4 CHALLENGES AND RECENT ADVANCES

Although graphene has excellent properties for application in different areas, there are inherent limitations. The main limitation is the lack of the bandgap, in that it that shortens its applicability in electronic devices. It is challenging for the scientific community to find ways to synthesize graphene in a reproducible manner and create a bandgap in graphene using various approaches. Additionally, there are efforts to intercalate graphene with other promising materials such as TMDs to create composites and heterostructures that can address some of the pressing issues and explore the possibilities for a new class of suitable materials.<sup>31</sup>

#### 1.10 TRANSITION METAL DICHALCOGENIDES

#### 1.10.1 STRUCTURE AND COMPOSITION

Two-dimensional TMDs have the formula  $MX_2$  (M = Mo, W; X = S, Se, Te). TMDs, unlike graphene, are semiconducting and therefore are suitable for electronic applications. Unlike other materials, TMDs can be easily exfoliated into monolayers. Their properties vary from material to material; for example,  $\text{MoS}_2$  is a low-bandgap (1.8 eV) material, making it suitable for different applications such as transistors and optoelectronic devices.<sup>32</sup>

#### 1.10.2 Properties

The 2D TMDs in their monolayer form are direct bandgap semiconductors, which are indirect bandgap semiconductors in the bulk form. Therefore, they are an excellent candidate for optoelectronic applications.<sup>33–35</sup> The monolayer form of TMDs is flexible and can be used in flexible electronic devices. The reasonably high electronic mobilities of the charge carriers in TMDs is good for their use in thin-film transistors.<sup>36</sup>

#### 1.10.3 APPLICATIONS

TMDs are low-bandgap materials, and therefore, they can absorb electromagnetic radiations of a lower energy. This makes them suitable candidates for photoluminescence, photodiodes, and other optoelectronic applications.<sup>35</sup> Transition metal oxides

have been in focus for their applications in electronics, such as FETs, high-switching devices, and power-efficient devices.<sup>37</sup>

Additionally, the 2D TMDs are mechanically flexible and suitable for wearable electronics as a result of their suitable electronic properties.<sup>37</sup> The thickness-dependent properties of TMDs have been exploited to design nonvolatile memories to enhance the performance of electronic devices.<sup>38</sup> TMDs have also found application in the emerging areas of catalysts in hydrogen evolution and storage solutions for a sustainable future.<sup>39</sup>

#### 1.10.4 CHALLENGES AND RECENT ADVANCES

TMDs have proven themselves to be promising materials for enhancing the functionality of electronic devices. But there are challenges, on which much progress is needed to encash the full potential of these promising materials. The main limiting factor is the challenge to scale the laboratory findings to an industrial scale to ramp up the production of TMDs-based electronic devices. These materials show excellent properties in small lab settings, but in larger areas, due to the variation in the thickness of these materials, a variation in the resultant properties has been observed. Another area of concern is the metal electrode and TMD interface/contact resistance in TMD-based devices. The resistance at the interface can adversely affect the performance of electronic devices. There have been efforts to grow large-area TMDs with uniform properties and minimize the contact resistance between TMDs and metal electrodes. Another approach is the development of heterostructures with graphene and other TMDs for advancing the use of heterostructures in multifunctional devices.

#### 1.11 LIMITATIONS OF TRADITIONAL MATERIALS FOR MODERN DEVICES: SCALING CHALLENGES IN THE CONTEXT OF MOORE'S LAW

In the 1960s, Moore presented an empirical law by which he predicted the advancement in the electronic industry and the revolutionizing of the ways of human interaction and knowledge and data creation, handling, and transmission. According to Moore's law, the number of transistors on a chip would double every two years. The relentless development of electronic devices has been keeping pace with the prediction of Moore's law for over six decades now. The exponential rise in the ability to integrate a considerable number of electronic components on a chip has led to electronic devices with higher computational power and lower costs and energy requirements at the same time. But as we are reaching the limits of integrating electronic components using traditional semiconducting materials, the need for more space and energy-efficient materials is growing. In the next section, we will delve into the limitations of traditional semiconducting materials vis-à-vis Moore's law and examine its effects on semiconductor technology.

#### 1.12 LIMITATIONS OF SILICON IN MODERN DEVICES

#### 1.12.1 Physical Scaling Limits of Silicon

As the size of electronic components decreases to sub-10 nm in electronic devices, quantum mechanical effects start taking prominence in the densely packed ICs. The quantum tunnelling effect is more pronounced when the thickness of the insulating layer is of the order of tens of nanometres in a transistor. As a result, the electron may tunnel across the insulating  $\mathrm{SiO}_2$  layer in the case of Si wafers, creating uncertain pathways of electron motion in the transistor, leading to increase in the leakage current. Quantum tunnelling compromises the switching ability of the transistor to turn off, thus increasing power requirements and lowering the efficiency of electronic devices. With the decrease in thickness of gate length, the ability of the electron to flow from the gate to the drain using gate voltage decreases, thus increasing the leakage and diminishing the performance of electronic devices.

#### 1.12.2 POWER DENSITY AND THERMAL DISSIPATION

With the increase in the density of components on a chip, the power density also increases, leading to challenges in thermal management. Due to the thermal conductivity of traditional semiconductors, there are issues in the management of heat generated during device operation. Additionally, the quantum effects that lead to the tunnelling of the charge carrier across the insulating barrier, especially in high-frequency operations, significantly contribute to heat generation. The common and traditional methods employed to cool electronic devices have their limitations, which can cause heat management issues in the devices and create performance instabilities.

#### 1.12.3 ELECTRICAL PERFORMANCE AND INTERCONNECT ISSUES

As the size of the component decreases, the performance of the metal wires, known as the interconnects, that connect different transistors becomes significant. With the decrease in the thickness of the interconnects, the resistivity of interconnects made of copper or aluminium increases, creating a critical bottleneck for charge transfer. Also, with the increase in the density of interconnects, the capacitance between the tightly packed interconnects increases. The combined effect of the increased resistivity and capacitance leads to resistive-capacitive (RC) delay in the circuit and many a time negates the increase in signal speed achieved for smaller components.

#### 1.13 THE FUTURE OF SEMICONDUCTOR TECHNOLOGY

There are many challenges for the semiconductor industry to keep up with the pace of development as envisaged by Moore's law. There are scaling challenges for the future of the electronic industry, and there are opportunities to meet those challenges with innovative approaches by employing new materials, device architectures, and manufacturing techniques. The use of new materials and technologies will change the industry and enable the application of these materials in the areas of artificial intelligence, quantum computing, and autonomous systems. The heterogeneous integration

of different systems into the same chip will help overcome the scaling limitations and allow the utilization of the properties of dissimilar materials to improve the performance of electronic devices. Quantum computing will open new avenues for the application of advanced technologies with greater computational power to perform intricate calculations in the frontier areas of science and technology.

#### 1.14 CONCLUSION

Semiconductor materials have played a vital role in the development of modern technology. They have enabled the creation of devices that have transformed our world, from computers and smartphones to solar cells and LEDs. The future of semiconductor materials is bright, with new and exciting applications being developed all the time.

Silicon's role as a traditional semiconductor material is deeply ingrained in the electronics industry. Its favourable properties, such as availability, moderate bandgap, and compatibility with MOSFET fabrication, have enabled its long-standing dominance. However, as technology progresses towards higher-performance applications, materials with better electronic and thermal properties are being explored for specialized uses. Despite this, silicon is expected to continue being a cornerstone of semiconductor technology for many years to come, especially in general-purpose computing and electronics.

Germanium, as one of the original semiconductor materials, played a crucial role in the early development of the electronics industry. While silicon has since overtaken germanium for most applications, germanium's superior electron and hole mobility, along with its infrared sensitivity, ensure that it remains relevant in high-speed, optoelectronic, and specialized applications. As innovative technologies emerge, germanium continues to be a valuable material for advanced semiconductor devices.

Gallium arsenide is a traditional semiconductor material that has proven invaluable in various advanced electronic and optoelectronic applications. Its direct bandgap, high electron mobility, and radiation resistance have made it a preferred material for high-frequency devices, MMICs, and space-based solar cells. While it faces competition from other semiconductor materials in certain areas, GaAs continues to hold a vital position in the semiconductor industry, particularly where high performance and specialized functionality are required.

Silicon carbide, gallium nitride, and indium phosphide represent the next generation of semiconductor materials, each offering unique advantages for high-power, high-frequency, and optoelectronic applications. SiC is ideal for power electronics, where its high efficiency and thermal stability enable more compact and reliable devices. GaN excels in high-frequency and high-power applications, making it a key material for RF amplifiers, power transistors, and communication systems. InP is the material of choice for high-speed and optical communication systems, where its high electron mobility and direct bandgap enable efficient data transmission.

While these materials present challenges in terms of cost and manufacturing, ongoing research and development are driving improvements in their performance and scalability. As the demand for more efficient, faster, and more reliable

semiconductor devices continues to grow, SiC, GaN, and InP are poised to play a critical role in shaping the future of electronics and communication technologies.

Graphene and TMDs represent the forefront of advanced semiconductor materials. Graphene's unparalleled conductivity, strength, and flexibility make it a strong candidate for various electronic, optical, and mechanical applications. However, its lack of a bandgap limits its use in digital electronics. On the other hand, TMDs offer the semiconducting properties required for switching devices, along with flexibility and strong photoluminescence, positioning them as prime candidates for next-generation electronics and optoelectronics.

As research continues, the combination of graphene, TMDs, and other 2D materials in heterostructures is likely to lead to breakthroughs in device performance and functionality. While challenges such as scalability and contact engineering remain, the future of these materials in the semiconductor industry is promising.